Samsung

Confidential

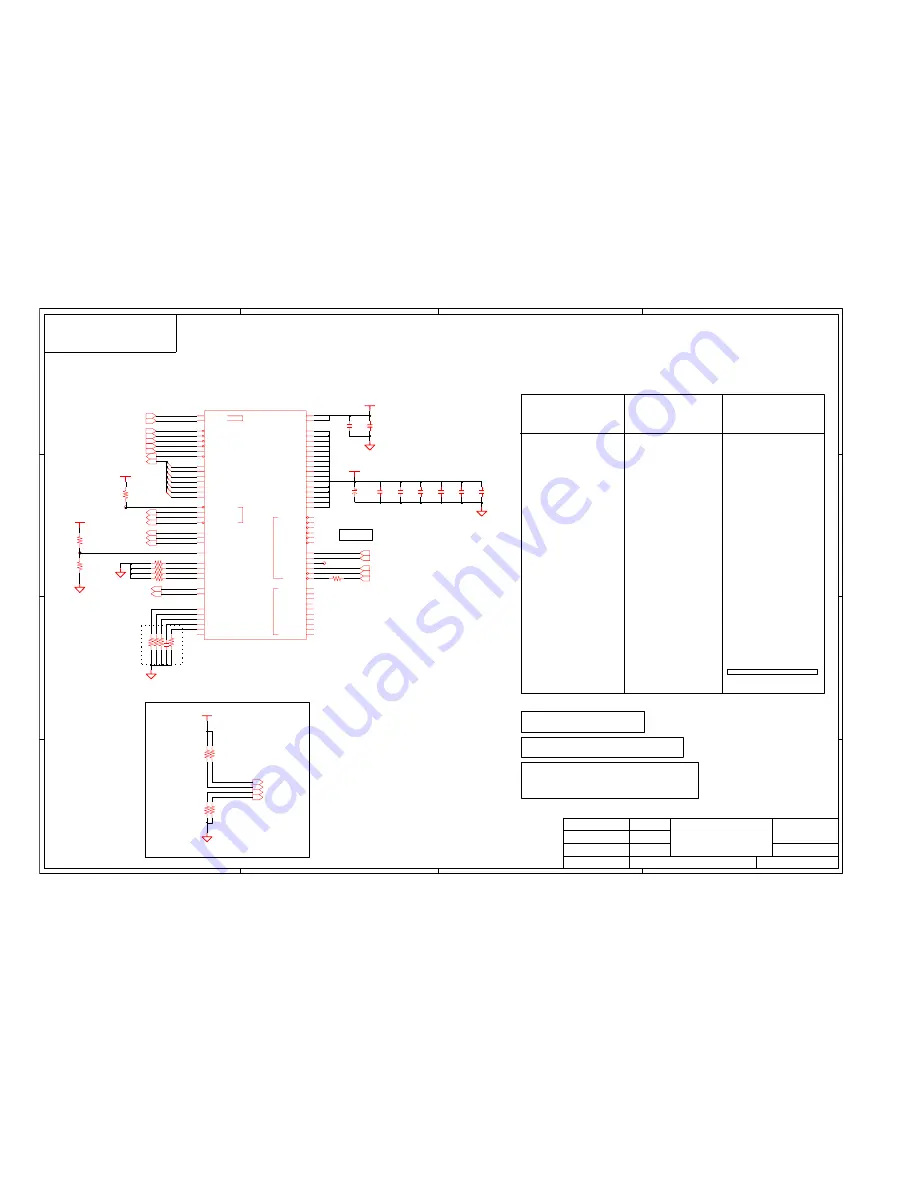

THERMAL

H CLK

XDP/ITP SIGNALS

3 / 4

RSVD

1.3125 V

0

0

1.5000 V

0

Voltage

1

1

0

1

1

1

1.4250 V

1

1.4875 V

0

0

0

0

1

1

1

0

0

0

1.3875 V

1

CPU Core Voltage Table

1.3250 V

0

0

1.3375 V

Observe 3:1 spacing b/w VCC/VSSsense lines and 25mil away

1

0

1

0

0

0

1

0

0

0

0

1

0

1

0

1

1

1

1.4500 V

1

0

0

1

0

1.4375 V

0

1

0

0

from each of the VCC/VSS test point vias.

0

0

0

0

1

0

1

0

0

0

0

1

1

1

1

1

0

0

1.1750 V

1

0

GTLREF : Keep the Voltage divider within 0.5"

1

1

0

0

0

0

1

0

0

0

0

0

1

Minimize coupling of any switching signals to this net.

0

0

1

0

0

1.3625 V

0

0

1

1.1375 V

1

1

1

1

1

1

1

0

0

1

of the first GTLREF0 pin with Zo=55ohm trace.

1

0

0

1

0

0

1

1

(preferred 50mil) from any other signal. And GND via 100mil away

0

1

0

0

1

0

1

0

1.3000 V

1

GND test points within 100mil of the VCC/VSSsense at the end of the line.

0

1

0

1.3750 V

1

0

1

1.1250 V

0

1.2375 V

0

1

1

0

0

0

1.3500 V

0

1

0

1

1

1

0

0

0

0

0

0

1

0

0

0

0

0

0

0

1

1

1

0

1

0

1

0

1

0

1

0

1

0

0

1

1

0

1

0

0

0

0

1

0

1.2875 V

1

0

0

0

1

0

0

1

0

0

0

1

PSI2*

0

0

0

1.4750 V

0

1.4625 V

0

trace shorter than 1/2" to their respective Banias socket pins.

0

0

0

0

1

0

1

0

1

0

1

1

0

0

1

1

1

0

1

0

0

1

0

1

1

0

1

0

1

VID(6:0)

1

0

0

*Yonah Processor (2.33 GHz / 800 MHz : TBD)

0

0.9625 V

0.9125 V

0

0.8875 V

1

0

1

0

1.2750 V

1

1.2625 V

1.2125 V

1.2000 V

1.1875 V

0

1

1

1.2500 V

0

1.2250 V

1

NO_STUFF

0

0

1

0

1

COMP0,2(COMP1,3) should be connected with Zo=27.4ohm(55ohm)

0

0

0

0

1

1

1

1

1

0

1

DPRSTP*

1

Route the VCC/VSSsense as a Zo=55ohm traces with equal length.

1

1

1

1

0

0.6000 V

1

1

1

1

0

0

0

0

0

0

1

0

1.4000 V

0

1

0

1

1

0.9000 V

1

0.8750 V

1

0.8250 V

1

0

1

0

0

0

0

0

0

1

0

0

0

1

0

0

0

0

0

0

0

0

0

1

0

1

1

1

0

1

1

1

0

Active

1

0

0

1

0

1

1

0.5875 V

0

0.5625 V

0

1

0

1

0

0

1

0

1.4125 V

1

0

0.9750 V

0.8500 V

1

0

1

1

1

0.8375 V

1

0.8125 V

1

1

0

1

1

1

0

1

0

0

0

0

1.1625 V

0

0

1

0

1

0

0

0

0

1

1

0.7375 V

0.7250 V

0

1

0

1

0

0

0

DPRSLPVR

1

0

1

0

0

1

1

0

1

0

1

1

0.5250 V

0

1

0

1

1

1

0.9875 V

1

1

1

1

0

0

0

1

1

VID(6:0)

0.9500 V

1

0.9250 V

0.8625 V

Voltage

0

0

0

0

1

1

0

0

0

1

0

1

0

0

0

0

1

0

1

0

0

0.6625 V

1

1

1

0

1

1

0

1

1

0

1

1

1

1

0.5750 V

0

0.5125 V

1

1

1

1

1

1

1

0

0

1

1

1

0

1

1

0

0

0

0

1

0

1.1500 V

0

0

0

0

1

1

0

0

0

1

0

0

0.6500 V

0

0

1

1

0

0

0

0.6125 V

0.7500 V

0

0

1

0

1

1

1

1

0

1

0

1

1

1

1

1

1

0

1

1

1

0

0

1

1

0

1

0

0

0

0

1

0

1

1

1

0

0

0

0

0

0

0

1

0

1

0.3250 V

0.3125 V

0

1

1

0.8000 V

1

1

0

0.7625 V

0

0.7000 V

0

0

0

0.6250 V

0

1

0

0

0

0

1

1

1

1

1

IMVP-6

0

0

0

0

0

1

0

1

1

1

0.5500 V

0.5375 V

1

1

0

0

0

0

1.0000 V

0

1

0

0

0

0

0

0

0

0.4750 V

0

0

1

0

0

0

0

0

VID(6:0)

0.3000 V

0

0.4250 V

0

0

1

0

0

0.7125 V

0

0.6875 V

0

1

0

1

1

1

1

1

1

1

1

1

1

0

0

0

1

1

1

0

0

0

1

0

1

1

0

0

0

1

0

0

1

1

1

0

1

1

1

0

1

0

0.4875 V

0

0.4625 V

1

0.9375 V

0

0

0

0

1

1

1

1

1

1

0.7875 V

0.7750 V

0

0

0

0

0

1

1

1

1

0

0.1875 V

0.1750 V

1

0.1250 V

0

1

1

0

1

0

1

1

1

1

1

1

0

1

1

1

1

1

1

1

0

0

0

1

0

1

0.0125 V

0

0

0

1

0

0

0

0

0

0.3375 V

0

0.4000 V

0.3875 V

0.3750 V

0.3625 V

1

1

0

0.4375 V

0

0.4125 V

0

0

1

1

1

0

1

1

0.6375 V

1

0

0

1

1

0.1625 V

1

0.1125 V

0

0.2375 V

1

0

0

0

1

0

0

1

1

1

1

1

0

0

1

1

0.0875 V

1

0.0625 V

0

0

0

0.0250 V

1

1

0.0000 V

1.0125 V

0

1.1125 V

0

0

0

0

0

1

1

0

0

0

1

0

1

1

1

1

1

0

0

1

1

0

0

0.6750 V

0

0

0.2500 V

0.2000 V

1.0875 V

1

1

0

1

0.1000 V

1

0.2250 V

0

0

0

0

1

1

1

1

1

0

1

1

1

1

1

1

0.0750 V

0

0.0500 V

0

1

0

0

0

0

B

Active/Deeper Sleep

A

1.1000 V

1

1

0

1

0

0

1

1

0

1

1

1

1

PSI2*

1

0.3500 V

Voltage

1

1

1

0

1

0

1

0.1375 V

1

1

PAGE

0

0

TITLE

1.0250 V

1

1

1

0.2125 V

0

1

1

1

1

DEV. STEP

REV

1

1

0

1

1

0

1

1

1

1

0

1

0

0

1.0500 V

1.0375 V

0.2750 V

0.0375 V

0

1

0

0

*"1111111" : 0V power good asserted.

0

1

1

0

1

1

1

1

0.0000 V

1

1

1

1

1

1

MODULE CODE

1

1

1

0.2875 V

1

1

1

1

0

3

1

SAMSUNG

ELECTRONICS

EXCEPT AS AUTHORIZED BY SAMSUNG.

0

1

1

0.0000 V

1

1

1

1

1

1

Dual Mode Region

LAST EDIT

1

1

1

0

1

PROPRIETARY INFORMATION THAT IS

1

1

1

0

1

0 or 1

1.0625 V

0.0000 V

1

PART NO.

0

1

1

1

0

NO_STUFF

1

1

0.4500 V

1

0

0

0.5000 V

1

0

0.0000 V

1

1

DPRSLPVR

0

1

0

1

1

Active Mode

1

0

0

1

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

0.0000 V

CHECK

0

1

1

2

OF

1

B

0

1

1

4

4

0

APPROVAL

3

1

DATE

1

1

1

SAMSUNG ELECTRONICS CO’S PROPERTY.

1

0

1

1

0.0000 V

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

1

DPRSTP*

Deeper Slp

A

0

1

COM-22C-015(1996.6.5) REV. 3

1

0

1

C

C

1

2

D

1

0

DRAW

Dual Mode Region

1

1

1

D

0

1

OXI Cap

Change to 270uF

Deeper Sleep/Extended Deeper Sleep

1

0 or 1

1

ITP DISABLE

0.0000 V

1

1

0

0.1500 V

1

0.2625 V

1.0750 V

1

11-C3

SUN XIAO

WUSHIJIANG

KEVIN LEE

6/26/2007

PV2

1.0

October 23, 2007 10:38:02 AM

BA41-XXXXX

11

58

Gevena

CPU

MEROM(2/3)

D:/tingting/geneva/Geneva_pr_1023

R597

0

11-C3

0

R654

1

R658

1%

27.4

6

2K

R661

1%

2

R657

56.2

60-B4

12-C4 60-B4

1%

10nF

C674

16V

VCCP_CORE

6.3V

10000nF

C673

C658

100nF

5

20-C1

13-B3

20-C1

8-C1

8-C1

VCCP_CORE

VCCP_CORE

54.9

R591

1%

R655

1%

1K

100nF

C640

R594

27.4

1%

R596

475

1%

11-A3

R653

1K

1%

11-C3

14-B1 20-C1 60-C4

11-A3

100nF

11-C3

C659

100nF

C660

100nF

C661

M21

VCCP_9

VCCSENSE

AF7

VID_0

AD6

AF5

VID_1

VID_2

AE5

VID_3

AF4

VID_4

AE3

VID_5

AF3

VID_6

AE2

VSSSENSE

AE7

100nF

C639

C26

VCCA_2

K6

VCCP_1

N21

VCCP_10

T21

VCCP_11

R21

VCCP_12

V21

VCCP_13

W21

VCCP_14

V6

VCCP_15

G21

VCCP_16

J6

VCCP_2

M6

VCCP_3

N6

VCCP_4

T6

VCCP_5

R6

VCCP_6

K21

VCCP_7

J21

VCCP_8

SLP*

D7

AC5

TCK

AA6

TDI

AB3

TDO

C23

TEST1

D25

TEST2

C24

TEST3

AF26

TEST4

AF1

TEST5

A26

TEST6

THERMTRIP*

C7

THRMDA

A24

THRMDC

B25

AB5

TMS

AB6

TRST*

B26

VCCA_1

GTLREF

AD26

AC2

PRDY*

AC1

PREQ*

PROCHOT*

D21

PSI*

AE6

PWRGOOD

D6

RSVD_1

D2

RSVD_10

C3

RSVD_2

F6

RSVD_3

D3

RSVD_4

D22

RSVD_5

M4

RSVD_6

N5

RSVD_7

T2

RSVD_8

V3

RSVD_9

B2

BCLK1

A21

AD4

BPM0*

AD3

BPM1*

AD1

BPM2*

AC4

BPM3*

BSEL0

B22

BSEL1

B23

BSEL2

C21

R26

COMP0

COMP1

U26

COMP2

AA1

COMP3

Y1

C20

DBR*

DPRSTP*

E5

DPSLP*

B5

DPWR*

D24

J1-3

MEROM-SOCKET

BCLK0

A22

54.9

1%

R659

C680

100nF

4

3

27.4

1%

R592

9-B4

20-C1

14-B1

13-B2

R593

40.2

1%

9-B4

R595

150

1%

1%

P1.5V

11-A3

11-A3

1K

R660

0

EC509

330uF

2.5V

AL

8-C4

22-D4

R652

8-C4

11-A4

0

60-B4

60-C4

11-A4

CPU1_TDI

CPU1_TMS

CPU1_TRST#

VCCP_CORE

60-B4

12-B4

11-A4

8-C4

CPU1_PSI#

CPU1_BSEL0

CPU1_BSEL1

CPU1_BSEL2

ITP3_DBRESET#

CPU1_VCCSENSE

CPU1_TCK

CPU1_PWRGDCPU

CPU1_DPSLP#

CPU1_SLP#

CPU1_VSSSENSE

CPU1_DPRSTP#

CPU2_THERMDA

CPU2_THERMDC

CPU1_THRMTRIP#

CPU1_DPWR#

CPU1_VID(6:0)

CLK0_HCLK0

CLK0_HCLK0#

CPU1_TCK

CPU1_TRST#

CPU1_TDI

CPU1_TMS

Содержание Geneva NP-R700 Series

Страница 230: ...4 29 This Document can not be used without Samsung s authorization 4 Troubleshooting ...

Страница 231: ...4 30 This Document can not be used without Samsung s authorization 4 Troubleshooting ...

Страница 236: ...4 35 9 Memory addition method This Document can not be used without Samsung s authorization 4 Troubleshooting ...