TPS-1 User’s Manual: Hardware

R19UH0081ED0107 Rev. 1.07

page 44 of 86

Jul 30, 2018

5.2. Loading and update of the firmware during the manufacturing process

The serial boot Flash can be written in several ways:

•

before mounting with a programmer,

•

via JTAG interface

Note1

,

•

via serial interface (UART)

Note1

,

•

via ETHERNET interface (BOOTP/TFTP)

Note2

Note

1

Basically we recommend to use serial interface (UART) during the development phase to fill an empty Flash.

2

via ETHERNET is for firmware update only. If you have TPS-1 toolkit v1.1.0.2 or later, please pre-program empty Flash with “default

image” in the toolkit before the Flash is soldered. It allows to do all required setting via ETHERNET.

5.2.1. UART interface (UART boot)

The UART interface is used for basic communication with the TPS-1. The interface is reduced to a minimum and has no modem lines.

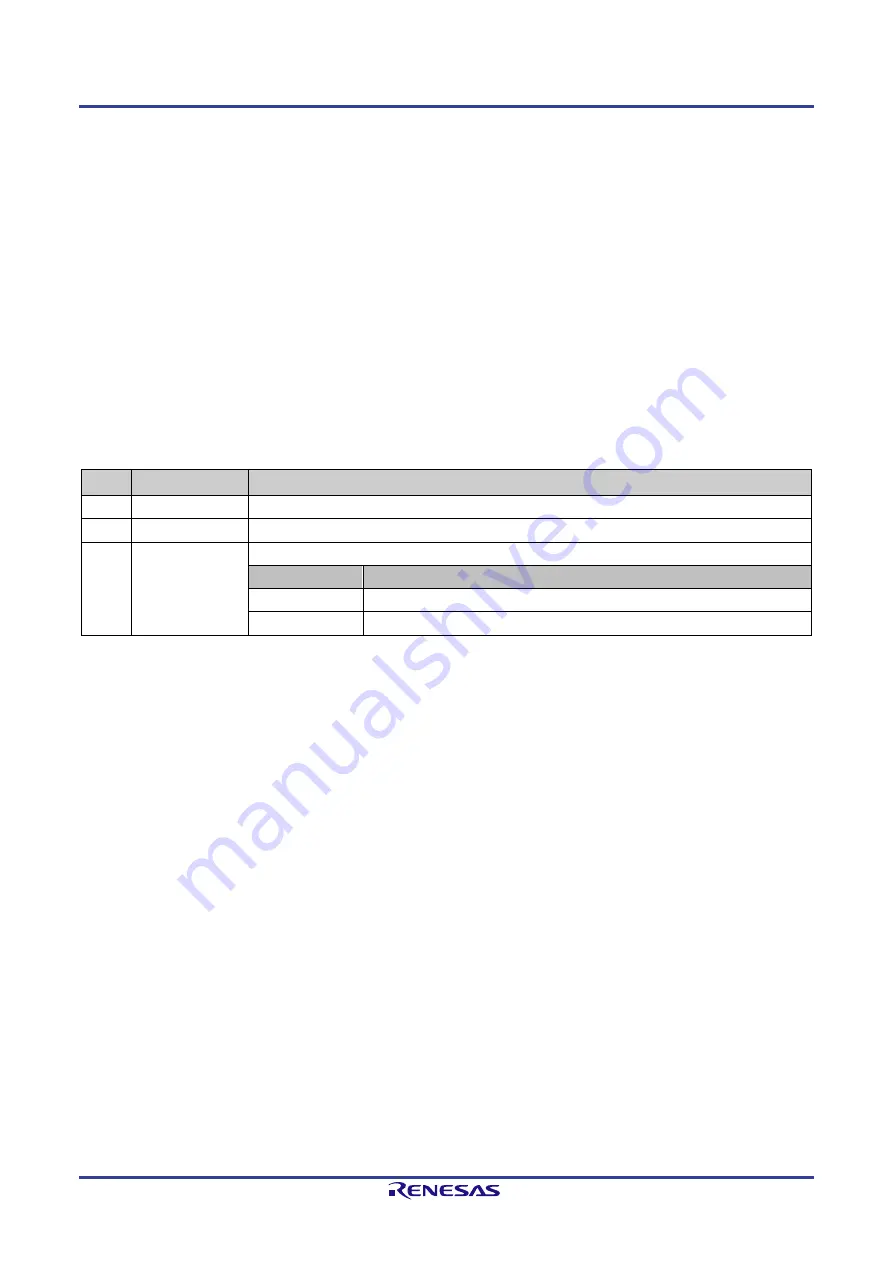

Table 5-1: Boot UART lines

Pin

Signal TPS-1

Description

C14

UART6_TX

Boot UART “Transmit data”

C13

UART6_RX

Boot UART “Receive data”

P12

BOOT_1

Forced Boot

Value

Function

0x0

BROM: Boot from Boot Flash is enabled (normal operating mode).

0x1

UART: Boot via UART is enabled.

The signal line BOOT_1 (Forced Boot) forces a firmware update. For this update, the UART interface is used. In this case also a corrupt version can be

updated.

The following parameters are set (fix) for the Interface:

•

Baudrate: 115200 baud

•

8-bit data length

•

1 stop bit

•

no parity check

•

no hardware flow control

Содержание TPS-1

Страница 91: ...TPS 1 R19UH0081ED0107 ...