M306V8T-EPB User’s Manual

4. Hardware Specifications

REJ10J0777-0100 Rev.1.00 2005.08.01

Page 67 of 90

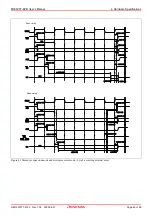

(2) Multiplex Bus Timing

Table 4.3 and Figure 4.2 show the bus timing in memory expansion mode and microprocessor mode (2-wait, accessing

external area, using multiplex bus).

Table 4.3 Memory expansion mode and microprocessor mode (2-wait, accessing external area, using multiplex bus)

Actual MCU

[ns]

This product

[ns]

Symbol Item

Min. Max. Min. Max.

td(BCLK-AD)

Address output delay time

50

See left

th(BCLK-AD)

Address output hold time (BCLK standard)

4

See left

th(RD-AD)

Address output hold time (RD standard)

(*1)

(*4)

th(WR-AD)

Address output hold time (WR standard)

(*1)

(*4)

td(BCLK-CS)

Chip-select output delay time

50

See left

th(BCLK-CS) Chip-select

output

hold

time (BCLK standard)

4

See left

th(RD-CS)

Chip-select output hold time (RD standard)

(*1)

See left

th(WR-CS)

Chip-select output hold time (WR standard)

(*1)

See left

td(BCLK-RD)

RD signal output delay time

40

See left

th(BCLK-RD)

RD signal output hold time

0

See left

td(BCLK-WR)

WR signal output delay time

40

See left

th(BCLK-WR)

WR signal output hold time

0

See left

td(BCLK-DB)

Data output delay time (BCLK standard)

50

See left

th(BCLK-DB)

Data output hold time (BCLK standard)

4

See left

td(DB-WR)

Data output delay time (WR standard)

(*2)

See left

th(WR-DB)

Data output hold time (WR standard)

(*1)

See left

td(BCLK-ALE)

ALE output delay time (BCLK standard)

40

See left

th(BCLK-ALE)

ALE output hold time (BCLK standard)

-4

See left

td(AD-ALE)

ALE output delay time (Address standard)

(*3)

See left

th(ALE-AD)

ALE output hold time (Address standard)

(*4)

See left

td(AD-RD)

After address RD signal output delay time

0

-25

td(AD-WR)

After address WR signal output delay time

0

-25

tdz(RD-AD) Address

output

floating start time

8

25

*1 Calculated by the following formula according to the frequency of BCLK.

)

(

10

5

.

0

9

BCLK

f

×

[ns]

*2 Calculated by the following formula according to the frequency of BCLK.

(

)

50

)

(

10

5

.

0

9

−

×

−

BCLK

f

n

[ns] n: "2" for 2-wait

*3 Calculated by the following formula according to the frequency of BCLK.

40

)

(

10

5

.

0

9

−

×

BCLK

f

[ns]

*4 Calculated by the following formula according to the frequency of BCLK.

15

)

(

10

5

.

0

9

−

×

BCLK

f

[ns]

Содержание Emulation Probe M306V8T-EPB

Страница 90: ...M306V8T EPB User s Manual...