Smart LTE Module Series

SC66 Hardware Design

SC66_Hardware_Design 77 / 139

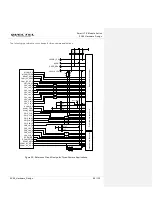

The following is a reference circuit design for dual camera applications:

CSI2_LN0_N

186

AI

MIPI data 0 signal of depth camera (-)

CSI2_LN0_P

185

AI

MIPI data 0 signal of depth camera (+)

CSI2_LN1_N

188

AI

MIPI lane 1 data signal of depth camera

(-)

CSI2_LN1_P

187

AI

MIPI lane 1 data signal of depth camera

(+)

CSI2_LN2_N

190

AI

MIPI lane 2 data signal of depth camera

(-)

CSI2_LN2_P

189

AI

MIPI lane 2 data signal of depth camera

(+)

CSI2_LN3_N

192

AI

MIPI lane 3 data signal of depth camera

(-)

CSI2_LN3_P

191

AI

MIPI lane 3 data signal of depth camera

(+)

MCAM_MCLK

99

DO

Rear camera clock signal

SCAM_MCLK

100

DO

Front camera clock signal

DCAM_MCLK

194

DO

Depth camera clock signal

MCAM_RST

74

DO

Rear camera reset signal

SCAM_RST

72

DO

Front camera reset signal

DCAM_RST

180

DO

Depth camera reset signal

MCAM_PWDN

73

DO

Rear camera PWDN signal

SCAM_PWDN

71

DO

Front camera PWDN signal

DCAM_PWDN

181

DO

Depth camera PWDN signal

CAM_I2C_SCL0

75

OD

I2C clock signal for rear and front

cameras

CAM_I2C_SDA0

76

OD

I2C data signal for rear and front camera

CAM_I2C_SCL1

196

OD

I2C clock signal for depth camera

CAM_I2C_SDA1

197

OD

I2C data signal for depth camera