Using PEX 8648 SMA Based (SI) Card White Paper – Version 1.3

© 2010 by PLX Technology, Inc. All Rights Reserved

11

8.1 Digital Loopback (Two Cards)

•

Step 1: Configuring port 3 on card #2 as the upstream port;

o

Plug card #2 in MB and boot the system.

o

Open PEX Device Editor (PDE)

o

Click on EEPROM editor.

o

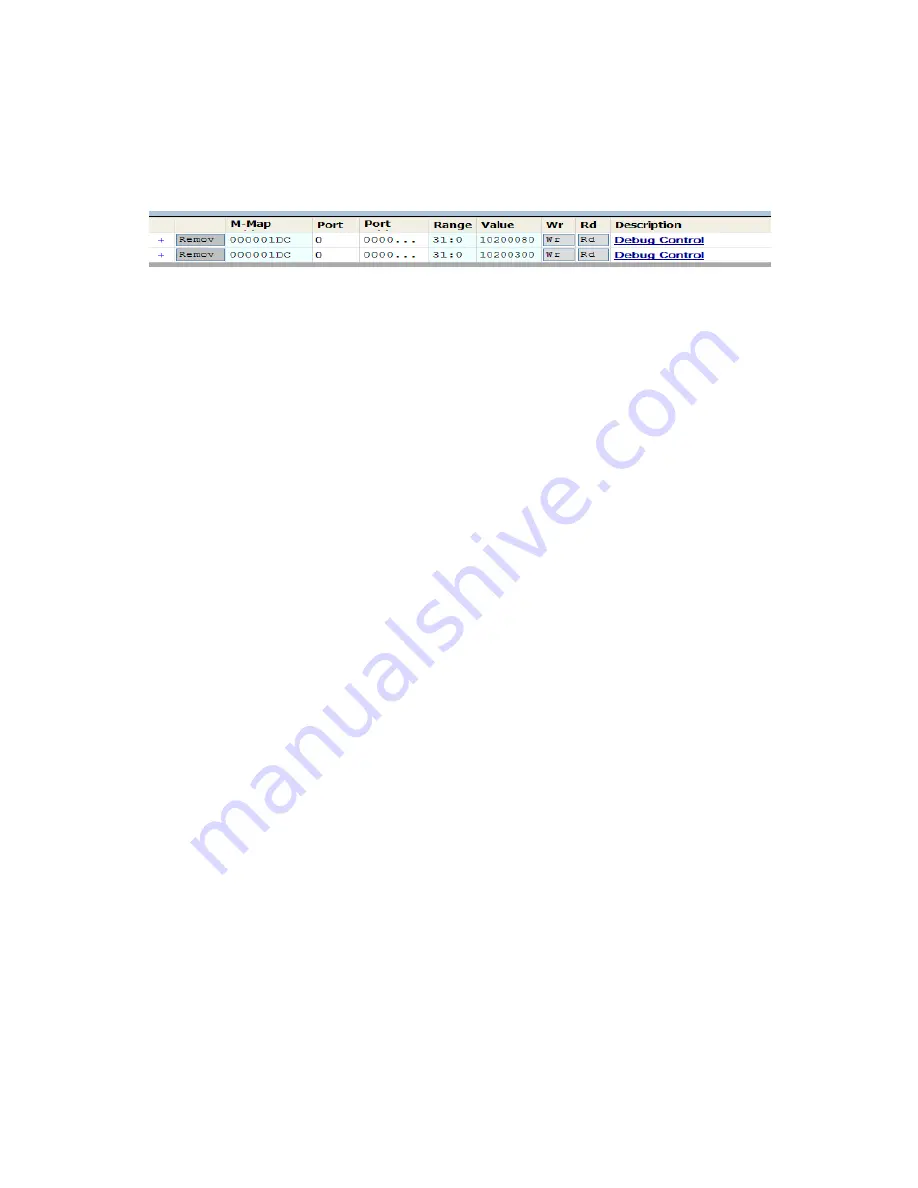

Add register 0x1dc (default value should be 0x10200080)

o

Add register 1dc again and program the value 0x10200300 (port 3 is upstream port).

o

Shut

down

system.

•

Step 2 -Install Cards

o

Remove card #2 from MB.

o

Plug card #1 in MB.

o

Plug card #2 in slot provided on card #1. This will provide power and clock to card #2.

o

Connect card #1 Port 3 to card #2 Port 3 by SMA coax cables (note cables are equal

length). Connect TX of card #1 to RX of card #2. Match Lane numbers. For x1, use Lane

0, for x2 use Lane 0 and Lane 1. (You can add backplane in the path once you have

verified that the initial setup works).

•

Digital Loopback Test

o

Reboot

system.

o

Link between both cards should be up. You will see port 3 LED on the cards blink.

o

Launch PDE and using memory map put port 3 in loopback. The following registers are

programmed on card #1 using memory map.

Program registers 0x210-0x21C with any pattern.

Set 0x230[12] to enable loopback on lanes 12-15.

Check to see if loopback is established, 0x230[15] = 1.

Set 0x228[31] to enable user pattern on lanes 12-15.

Check 0x244 “SerDes quad 3 diagnostic data” for error count. This should be

zero.

Change pattern in register 0x210.

Check 0x244. You should see error count.

Reset bits 0x228[31], 0x254[19] and 0x230[12].

Reboot

system

Repeat test with backplane in path. Change SerDes settings and check for error counts.