DVR-3100-S

101

5

7

8

5

7

8

C

D

F

A

B

E

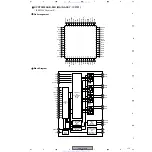

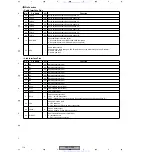

• 96kHz 24 bit

∆∑

ADC

AINL

AINR

1

∆∑

Modulator

2

AINR

∆∑

Modulator

1

VCOM

DIF

SCLK

SDTO

LRCK

MCLK

Voltage

Reference

Decimation

Filter

Decimation

Filter

Serial I/O

Interface

Clock

Divider

4

14

10

12

9

11

DGND

8

VD

7

AGND

5

VA

6

PDN

13

CKS0

16

CKS1

3

CKS2

15

AINL

2

CKS1

3

VCOM

4

AGND

5

VA

6

VD

7

DGNS

8

16

CKS0

15

CKS2

14

DIF

13

PDN

12

SCLK

11

MCLK

10

LRCK

9

SDTO

No.

Pin Name

I/O

Function

1

AINR

I

R ch analog input

2

AINL

I

L ch analog input

3

CKS1

I

Mode select 1

4

VCOM

O

Common voltage output, bias voltage of VA/2 and ADC input

5

AGND

−

Analog ground

6

VA

−

Analog power supply, 4.5V to 5.5V

7

VD

−

Digital power supply, 2.7 to 5.5V (fs = 4k to 48kHz), 3.0 to 5.5V (fs = 48k to 96kHz)

8

DGND

−

Digital ground

9

SDTO

O

Audio serial data output, outputs "L" in the power down mode.

10

LRCK

I/O

Channel clock I/O, outputs "L" by master mode in the power down mode.

11

MCLK

I

Master clock input

12

SCLK

I/O

Audio serial data clock, outputs "L" by master mode in the power down mode.

13

PDN

I

Power down mode "H": power up, "L": power down

14

DIF

I

Audio interface format, "H" : 24 bit I2S compatibility, "L" : 24 bit MSB justify

Mode select 2

Mode select 0

AK5381VT (MAIN ASSY : IC3101)

Pin Function

Pin Arrangement (Top view)

Block Diagram

www. xiaoyu163. com

QQ 376315150

9

9

2

8

9

4

2

9

8

TEL 13942296513

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299