7.

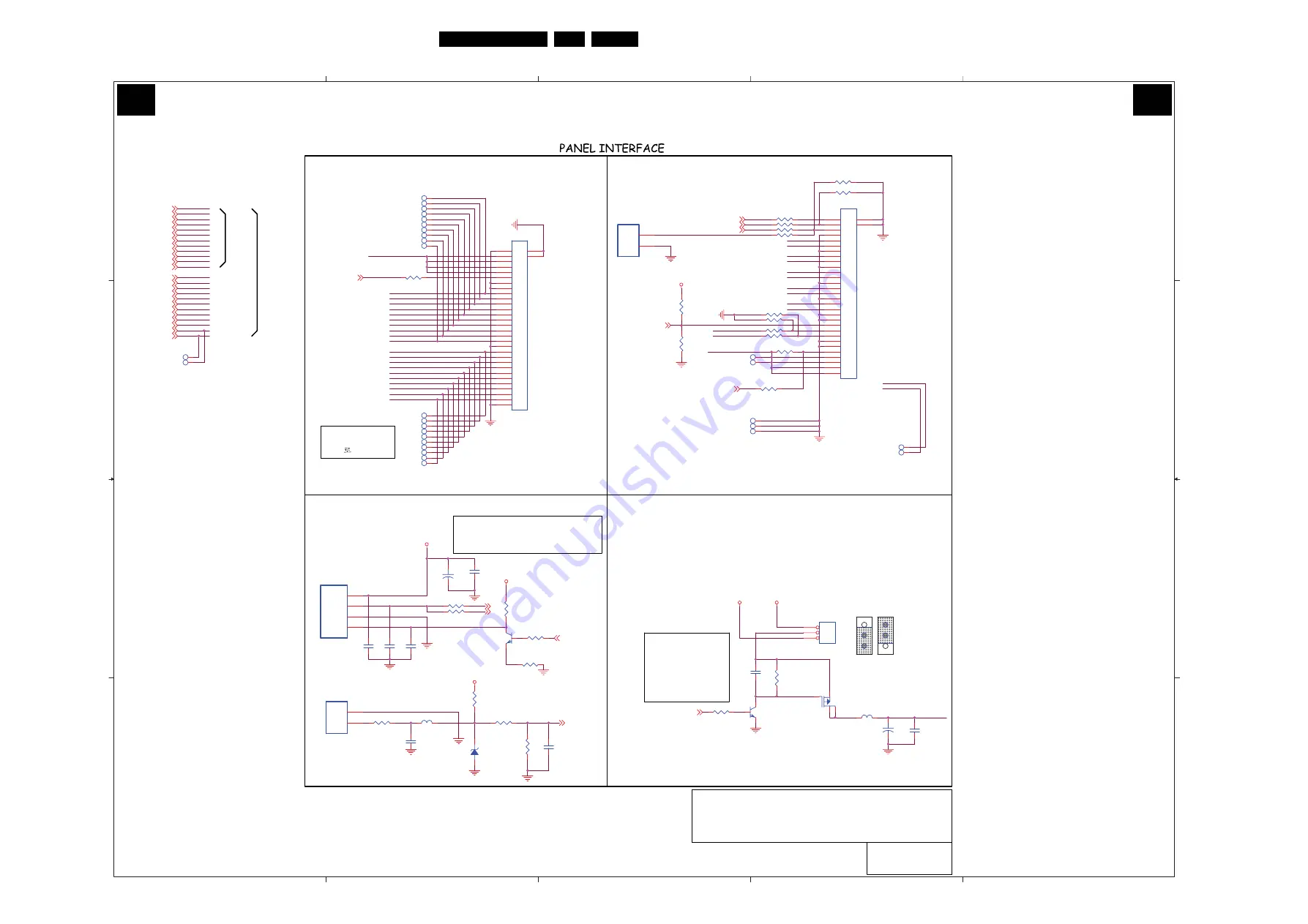

Circuit Diagrams and PWB Layouts

Main Board: LVDS Output

5

5

4

4

3

3

2

2

1

1

D

D

C

C

B

B

A

A

INTERNAL

S

INGLE

LV

D

S

_OUT

PANEL POWER OPTION

- 12V : LG

- 5V :

SS

/CMO

PNLON

- High : ON

- Low : OFF

IR&KEY_-PAD(PROFILO_KEY&IR)

F

S

CLK+, F

S

CLK-

different

a

il

p

a

ir

ro

u

ting

INTERNAL

D

U

A

L

L

V

D

S

_OUT

DUAL_LVD

S

_OPTION

LCD_PANEL PWR CONTROL

S

INGLE_LVD

S

_OPTION

LG

3

2" A6K6

ACD : DCR

ON/OFF

CMO

3

2" Control Pin De

s

cription

s

RPF: Di

s

pl

a

y Rot

a

tion (Low -> Norm

a

l, High -> 1

8

0 Degree

s

)

*

Overdrive Look

u

p t

ab

le

OD

S

EL1 : Low, OD

S

EL2 : Low -> Optimized for 60Hz fr

a

me r

a

te

OD

S

EL1 : High, OD

S

EL2 : Low -> Optimized for 50Hz fr

a

me r

a

te

1)

S

PEAKER : BLUE ==> CN4

2) IDTV POWER : RED ==> CN19

3

) IR : WHITE ==> CN20

4) IDTV DOWNLOAD : BLACK ==> CN15

12V 5V

TXE0-

TXE0+

TXE1-

TXE1+

TXE2-

TXE2+

TXEC-

TXEC+

TXE

3

-

TXE

3

+

TXE4-

TXE4+

TXE

3

-

TXE2-

TXE0-

TXE0+

TXO0-

TXE2+

TXOC-

TXO2-

TXEC-

TXO1-

TXE

3

+

5V/12V_MOD

TXEC+

TXE1-

TXO2+

TXOC+

TXE1+

TXO

3

+

TXO1+

TXO0+

TXO

3

-

TXOC+

TXO1-

TXO4-

TXO0+

TXOC-

TXO4+

TXO0-

TXO2+

TXO

3

+

TXO2-

TXO

3

-

TXO1+

5V/12V_MOD

TXE4+

TXE4-

TXE4-

TXE4+

TXE0+

TXE1-

TXE1+

TXE0-

TXE2-

TXE2+

TXE

3

+

TXEC-

TXE

3

-

TXEC+

5V/12V_MOD

LED_R_IN

V

b

r_O

u

t

LCD_ON/OFF

4

TXE0-

4

TXE0+

4

TXE1-

4

TXE1+

4

TXE2-

4

TXE2+

4

TXEC-

4

TXEC+

4

TXE

3

-

4

TXE

3

+

4

TXE4-

4

TXE4+

4

OD

S

EL1

4

TXO

3

+

4

TXO2-

4

TXO0-

4

TXO4+

4

TXO2+

4

TXOC+

4

TXO0+

4

TXOC-

4

TXO

3

-

4

TXO1-

4

TXO1+

4

TXO4-

4

IR

4

LED_R

4

D_IR

3

LG_

S

EL_DCR

4

OD

S

EL1

4

RPForEXT_V

b

r

4

PANEL_

S

YNC

4

ADC-IN1

4

RPForEXT_V

b

r

4

V

SS3

V

V

SS

5

V

SS3

V

5VD

12VD

V

SS

5

R605

0R

R552

0R(NU)

1

2

JTP6

3

1

R269

150R

1

2

TP19

1

R611

0R(NU)

R551

0R(NU)

1

2

R602

0R(NU)

CN20

J

S

T250-4P

1

2

3

4

5V_

S

T-BY

IR

GND

LED_ERD

JTP

8

2

1

JTP72

1

R270

1K

1

2

JTP70

1

R497

560

1

2

JTP79

1

R266

100R

R594

0R

1

2

JTP6

8

1

JTP40

1

JTP77

1

FB7

UPB201209T-500Y-

S

JTP

3

2

1

JTP41

1

C

3

92

100nF

JTP66

1

Q12

MMBT

3

904

1

3

2

JTP75

1

R444

100(NU)

R499

33

0

1

2

JP1

HEADER_

3

X1

1

2

3

5V

P

a

nel

12V

J10

12507WR-

3

0A01(NU)

1

2

3

4

5

6

7

8

9

10

11

12

1

3

14

15

16

17

1

8

19

20

21

22

2

3

24

25

26

27

2

8

29

3

0

3

1

3

2

+

C151

220

u

F/16V

1

2

JTP64

1

C46

8

22pF

1

2

JTP7

3

1

R556

0R(NU)

1

2

C470

100nF

1

2

R265

3

.

3

K

+

C

3

91

100

u

F/16V

1

2

R557

0R(NU)

1

2

JTP

83

1

C469

100nF

1

2

C152

100nF

C467

100nF

1

2

JTP2

8

1

R599

1.2K

1

2

JTP71

1

R495

0R

1

2

JTP

8

0

1

Q11A

IRF7

3

14

1

2

7

8

C150

100nF

JTP29

1

J7

12507WR-

3

0A01

1

2

3

4

5

6

7

8

9

10

11

12

1

3

14

15

16

17

1

8

19

20

21

22

2

3

24

25

26

27

2

8

29

3

0

3

1

3

2

FB70

UPB201209T-500Y-

S

JTP69

1

JTP

3

0

1

JTP7

8

1

D1

3

1.

8

V_ZENER

1

2

R60

3

0R(NU)

R55

3

1K(NU)

1

2

CN21

J

S

T250-2P

1

2

GND

KEY

JTP

3

1

1

R604

0R(NU)

JTP67

1

JTP76

1

R555

0R

1

2

Q1

3

MMBT

3

904

1

3

2

R49

8

0R

1

2

C

3

9

3

100nF

1

2

R550

0R(NU)

1

2

R496

0R

1

2

CN24

J

S

T250-2P

1

2

GND

V

b

r_O

u

t

R55

8

0R

1

2

JTP65

1

TP1

8

1

JTP74

1

R554

0R

1

2

B5

B5

H_17490_005.ep

s

3

11007

LVD

S

OUTPUT

Содержание TES2.0E

Страница 9: ...Mechanical Instructions EN 9 TES2 0E LA 4 Figure 4 3 Exploded View 32 sets H_17490_015 eps 291007 ...

Страница 10: ...Mechanical Instructions EN 10 TES2 0E LA 4 Figure 4 4 Exploded View 42 sets H_17490_016 eps 291007 ...

Страница 26: ...EN 26 TES2 0E LA 7 Circuit Diagrams and PWB Layouts Layout Main Board Top Side H_17490_009 eps 161007 ...