123

8175 N/B MAINTENANCE

8175 N/B MAINTENANCE

5.3 Intel 82801BA(I/O Controller HUB )

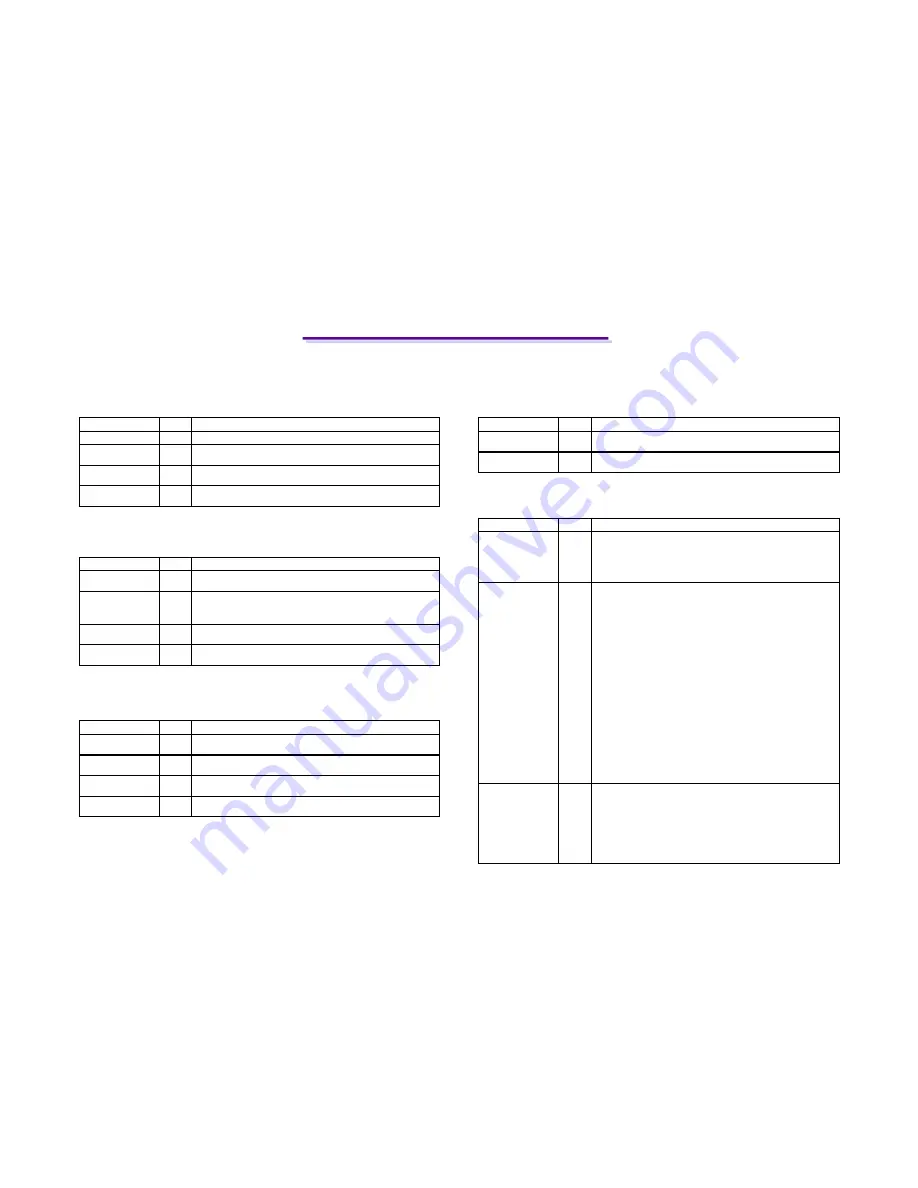

Hub Interface Signals

Name Type

Description

HL[11:0]

I/O

Hub Interface Signals

HL_STB

I/O

Hub Interface Strobe:

One of two differential strobe signals used to

transmit and receive data through the hub interface.

HL_STB#

I/O

Hub Interface Strobe Complement:

Second of the two differential

strobe signals.

HLCOMP

I/O

Hub Interface Compensation:

Used for hub interface buffer

compensation.

LAN Connect Interface Signals

Name Type

Description

LAN_CLK

I

LAN Interface Clock:

This signal is driven by the LAN Connect

component. The frequency range is 0.8 MHz to 50 MHz.

LAN_RXD[2:0]

I

Received Data:

The LAN Connect component uses these signals to

transfer data and control information to the integrated LAN

Controller. These signals have integrated weak pull-up resistors.

LAN_TXD[2:0]

O

Transmit Data

: The integrated LAN Controller uses these signals to

transfer data and control information to the LAN Connect component.

LAN_RSTSYNC

O

LAN Reset/Sync:

The LAN Connect component’s Reset and Sync

signals are multiplexed onto this pin.

EEPROM Interface Signals

Name Type

Description

EE_SHCLK

O

EEPROM Shift Clock:

EE_SHCLK is the serial shift clock output to

the EEPROM.

EE_DIN

I

EEPROM Data In:

EE_DIN transfers data from the EEPROM to the

ICH2. This signal has an integrated pull-up resistor.

EE_DOUT

O

EEPROM Data Out:

EE_DOUT transfers data from the ICH2 to the

EEPROM.

EE_CS

O

EEPROM Chip Select:

EE_CS is a chip-select signal to the

EEPROM.

Firmware Hub Interface Signals

Name Type

Description

FWH[3:0]

/

LAD[3:0]

I/O

Firmware Hub Signals:

These signals are muxed with LPC address

signals.

FWH[4]

/

LFRAME#

I/O

Firmware Hub Signals:

This signal is muxed with LPC LFRAME#

signal.

PCI Interface Signals

Name Type

Description

AD[31:0]

I/O

PCI Address/Data:

AD[31:0] is a multiplexed address and data bus.

During the first clock of a transaction, AD[31:0] contain a physical

address (32 bits). During subsequent clocks, AD[31:0] contain data.

The ICH2 drives all 0s on AD[31:0] during the address phase of all

PCI Special Cycles.

C/BE[3:0]#

I/O

Bus Command and Byte Enables:

The command and byte enable

signals are multiplexed on the same PCI pins. During the address

phase of a transaction,C/BE[3:0]# define the bus command. During

the data phase, C/BE[3:0]# define the

Byte Enables.

C/BE[3:0]# Command Type

0000 Interrupt Acknowledge

0001 Special Cycle

0010 I/O Read

0011 I/O Write

0110 Memory Read

0111 Memory Write

1010 Configuration Read

1011 Configuration Write

1100 Memory Read Multiple

1110 Memory Read Line

1111 Memory Write and Invalidate

All command encodings not shown are reserved. The ICH2 does not

decode reserved values, and therefore will not respond if a PCI master

generates a cycle using one of the reserved values.

DEVSEL#

I/O

Device Select:

The ICH2 asserts DEVSEL# to claim a PCI

transaction. As an output, the ICH2 asserts DEVSEL# when a PCI

master peripheral attempts an access to an internal ICH2 address or an

address destined for the hub interface (main memory or AGP). As an

input, DEVSEL# indicates the response to an ICH2- initiated

transaction on the PCI bus. DEVSEL# is tri-stated from the leading

edge of PCIRST#. DEVSEL# remains tri-stated by the ICH2 until

driven by a target device.