MeiG

Product

Manual

of

SLM750

Module

SLM750

Module

Hardware

Design

Page 54, total 84 pages

signal.

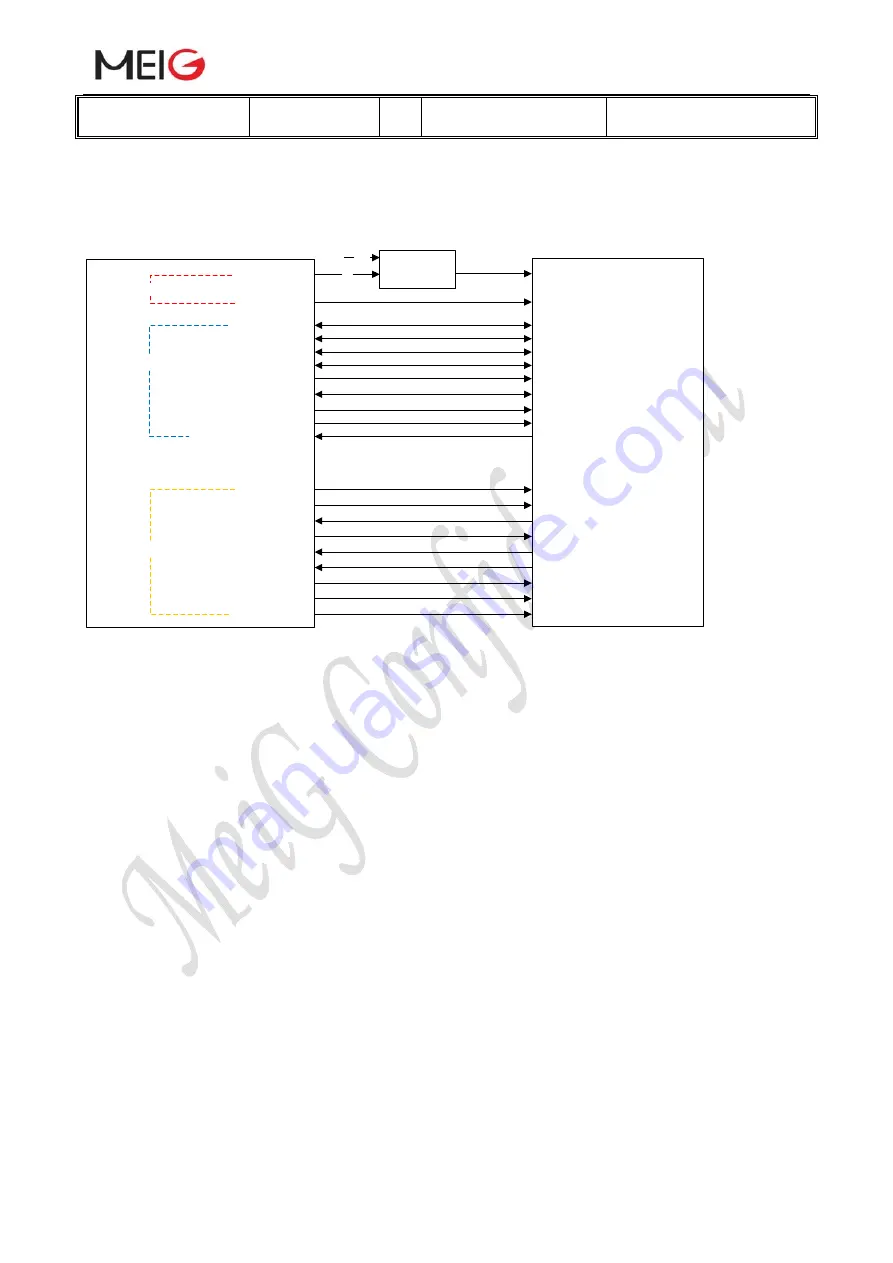

The following figure shows a reference design of Wireless Connectivity interfaces with

SLM158 module.

Module

SLM158Module

DCDC/LDO

EN

PM_EMBLE

VDD_EXT

SDC1_DATA3

SDC1_DATA1

SDC1_DATA0

SDC1_DATA2

SDC1_CLK

SDC1_CMD

WLAN_EN

WLAN_SLP_CLK

WAKE_ON_WIRELESS

BT_EN

BT_UART_RTS

BT_UART_CTS

BT_UART_TXD

BT_UART_RXD

PCM_IN

PCM_OUT

PCM_SYNC

VDD_3V3

VIO

VCC

PCM_CLK

SDC1_DATA3

SDC1_DATA1

SDC1_DATA0

SDC1_DATA2

SDC1_CLK

SDC1_CMD

WLAN_EN

WLAN_SLP_CLK

WAKE_ON_WIRELESS

BT_EN

BT_UART_CTS

BT_UART_RTS

BT_UART_RXD

BT_UART_TXD

PCM_OUT

PCM_IN

PCM_SYNC

PCM_CLK

POWER

WLAN

Bluetooh

Figure 24 Reference Circuit of Wireless Connectivity Interfaces with SLM158

Note:

1. SLM158 can only be used as slave equipment.

2. When SLM750 modules enable Bluetooth, PCM_SYNC and PCM_CLK are used only for

signal output.

3. The 24~27 pin is a multiplexed pin, which can be used for Codec voice or PCM connected

to SLM750V to realize Bluetooth voice communication.

4. *functionality is pending for development

3.17.1 WLAN Interface

SLM750 provides a low power SDIO 3.0 interface and control interface for WLAN design.

SDIO interface supports Single data rate mode, it maximum frequency is 50MHz.

As SDIO signals are very high-speed, in order to ensure the SDIO interface design corresponds

with the SDIO 3.0 specification, please comply with the following principles:

It is important to route the SDIO signal traces with total grounding. The impedance of SDIO