MeiG

Product

Manual

of

SLM750

Module

SLM750

Module

Hardware

Design

Page 27, total 84 pages

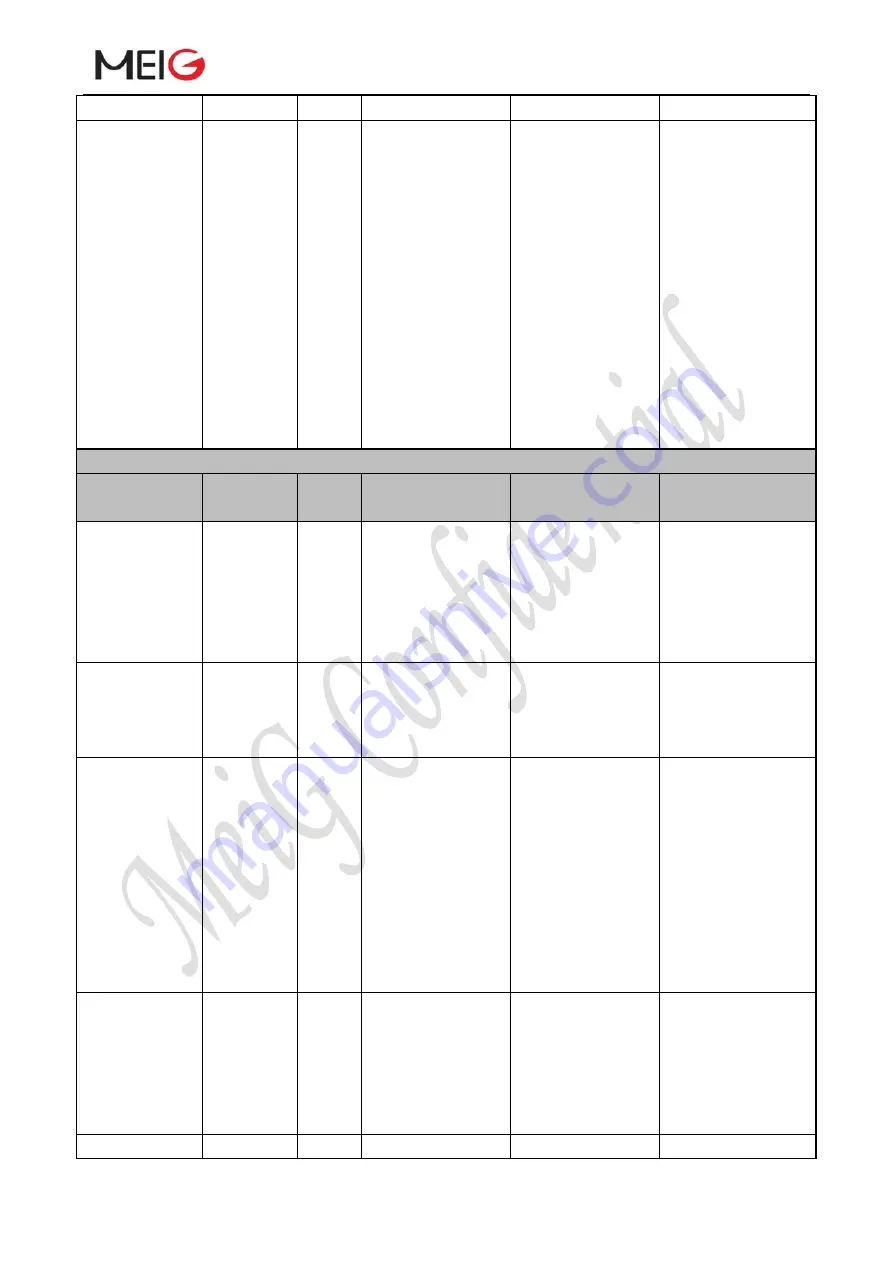

VIHmax=3.34V

SD_DATA0

31

IO

SD card SDIO

signal data line 0

1.8V SD card:

VOLmax=0.45

VOHmin=1.4V

V ILmin=-0.3V

VILmax=0.58V

VIHmin=1.27V

VIHmax =2.0V

3.0V SD card:

VOLmax=0.38V

VOHmin=2.01V

V ILmin=-0.3V

VILmax=0.76V

VIHmin=1.72V

VIHmax=3.34V

Refer to SD3.0

protocol. If

unused, keep it

open.

SGMII Pin

Pin name

Pin

number

I/O

Description

DC features

Note

EPHY_RST_

N*

119 DO

Ethernet

PHY

reset

For 1.8V:

VOLmax=0.45V

VOHmin=1.4V

For 2.85V:

VOLmax=0.35V

VOHmin =2.14V

1.8V /2.85V power

domain.

If unused, keep it

open.

EPHY_INT_N

*

120 DI

Ethernet

PHY

interruption

VILmin=-0.3V

VILmax=0.6V

VIHmin=1.2V

VIHmax=2.0V

1.8V /2.85V power

domain.

If unused, keep it

open.

SGMII_MDA

TA*

121 IO

SGMII

MDIO

data

For 1.8V:

VOLmax=0.45V

VOHmin=1.4V

VILmax =0.58V

VIHmin =1.27V

For 2.85V:

VOLmax=0.35V

VOHmin =2.14V

VILmax =0.71V

VIHmin =1.78V

1.8V/2.85V power

domain.

If unused, keep it

open.

SGMII_MCL

K*

122 DO

SGMII

MDIO

clock

For 1.8V:

VOLmax=0.45V

VOHmin=1.4V

For 2.85V:

VOLmax=0.35V

VOHmin =2.14V

USIM2_VDD

128 PO

SGMII

MDIO

-

1.8V/2.85V

power