8

dc2071afc

DEMO MANUAL DC2071A

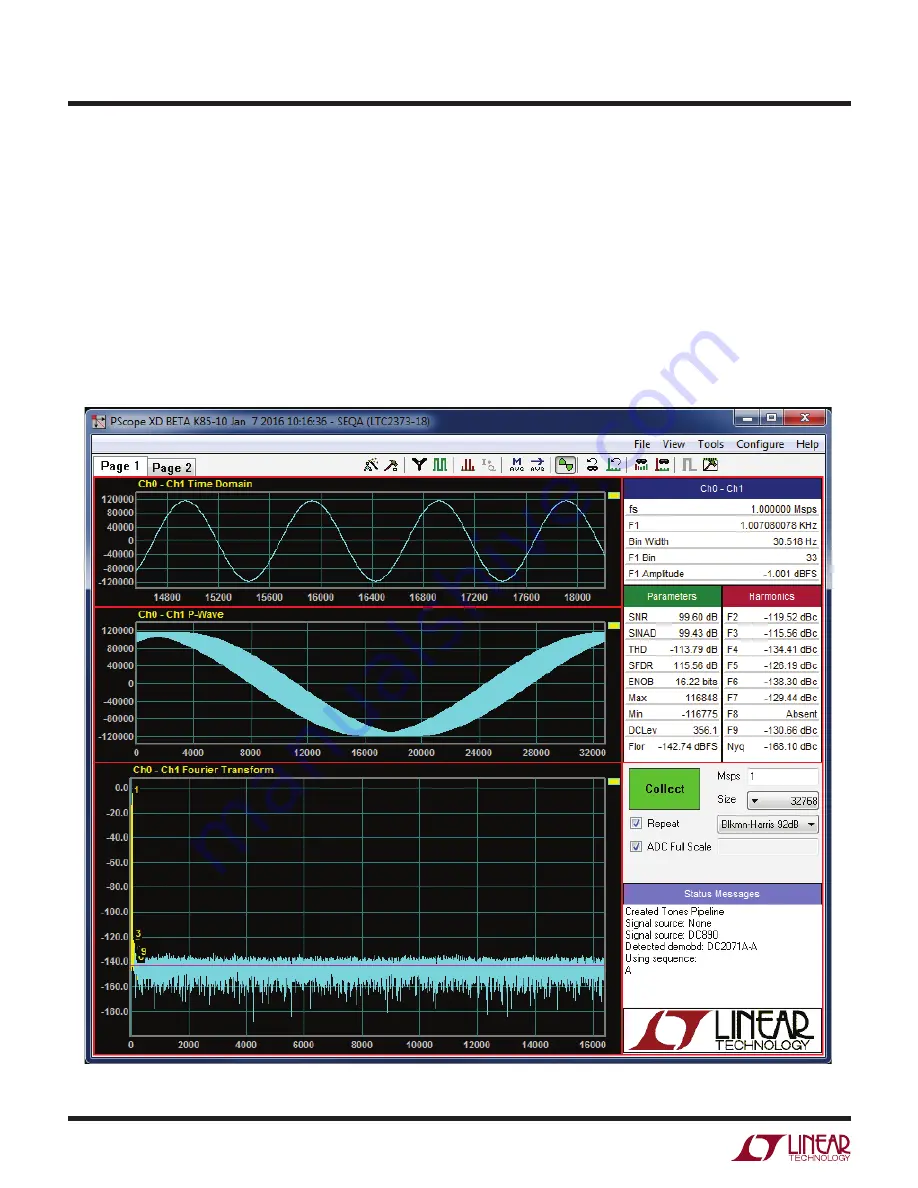

DC890 Data Collection

For SINAD, THD or SNR testing, a low noise, low distortion

generator such as the B&K Type 1051 or Stanford Research

SR1 should be used. A low jitter RF oscillator such as the

Rohde & Schwarz SMB100A or DC1216A-A high speed

clock source is used to drive the clock input. This demo

board is tested in-house by attempting to duplicate the

FFT plot shown in the Typical Performance Characteristics

section of the LTC2373-18 data sheet. This involves using

a 62MHz clock source, along with a sinusoidal generator

at a frequency of approximately 1kHz. The input signal

level is approximately –1dBFS. A typical FFT obtained

with DC2071A is shown in Figure 7. Note that to calculate

the real SNR, the signal level (F1 amplitude = –1.001dB)

has to be added back to the SNR that PScope displays.

With the example shown in Figure 7 this means that the

actual SNR would be 100.60dB instead of the 99.60dB that

PScope displays. Taking the RMS sum of the recalculated

SNR and the THD yields a SINAD of 100.4dB which is fairly

close to the typical number for this ADC.

Figure 7. PScope Screen Shot

DC2071A SETUP