THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

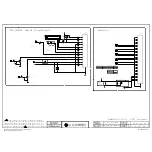

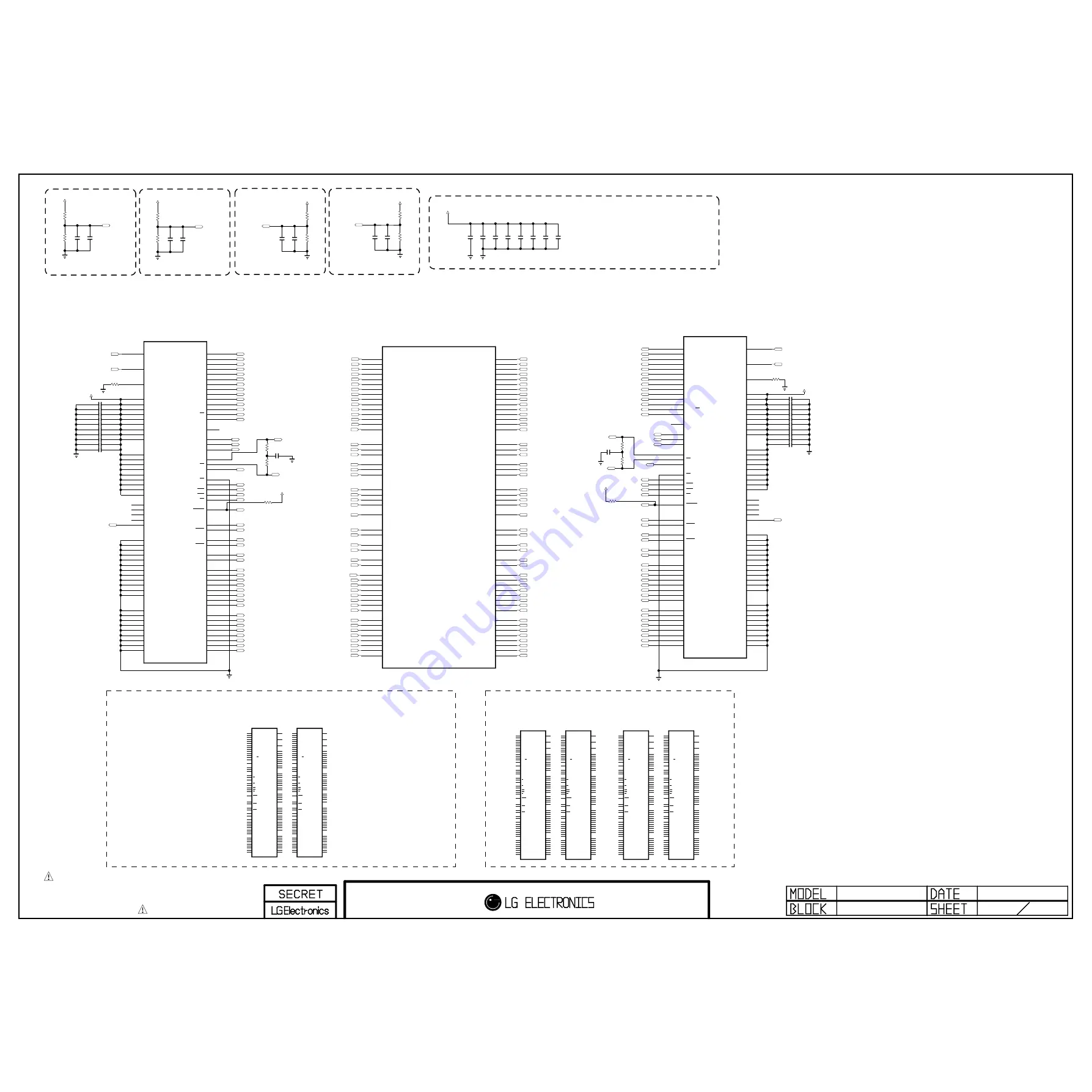

DDR

12 12

B-MDQL3

B-MDQSU

H5TQ2G63DFR-PBC

IC1201-*4

BR/ASIA(DDR_2G_1600_HYNIX)

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

A13

T3

NC_5

M7

BA0

M2

BA1

N8

BA2

M3

CK

J7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J1

NC_2

J9

NC_3

L1

NC_4

L9

NC_6

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J2

VSS_6

J8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

A-MA9

A-MDQU1

A-MDQU2

B-MDQL1

H5TQ1G63EFR-PBC

IC1201-*1

DDR_1600_HYNIX_9003(DEV)

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

NC_7

T3

NC_5

M7

BA0

M2

BA1

N8

BA2

M3

CK

J7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J1

NC_2

J9

NC_3

L1

NC_4

L9

NC_6

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J2

VSS_6

J8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

+1.5V_DDR

A-MDQL5

A-MDQL7

B-MA6

R1227

1K

1%

B-MDQU5

B-MRASB

A-MA8

C1250

0.1uF

C1215

0.1uF

B-MDQL2

B-MA3

B-MA11

A-MA7

+1.5V_DDR

A-MA11

B-MDQL5

B-MBA1

+1.5V_DDR

C1230

0.1uF

B-MWEB

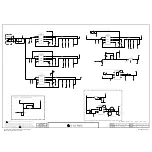

K4B2G1646E-BCK0

IC1202-*5

(OPT)(DDR_2G_1600_SS)

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

A13

T3

NC_5

M7

BA0

M2

BA1

N8

BA2

M3

CK

J7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J1

NC_2

J9

NC_3

L1

NC_4

L9

NC_6

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J2

VSS_6

J8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

A-MDQL0

B-MDQU4

C1227

10uF

A-MRESETB

C1217

1uF

B-MDQSLB

C1211

0.1uF

B-MDQU3

B-MDQL7

A-MBA0

C1236

0.1uF

A-MA12

B-MDQU6

A-MA2

A-MCK

C1219

1uF

A-MA1

C1228

0.1uF

B-MDQL6

A-MA13

B-MA10

A-MA3

A-MDQL7

A-MDQL1

A-MA14

R1205

1K

1%

A-MA11

B-MDQL1

B-MBA0

A-MBA1

B-MWEB

B-MDQL0

+1.5V_DDR

B-MDQU7

A-MDQSU

A-MDQU0

A-MVREFDQ

B-MA8

B-MCKE

B-MA12

R1225

1K

1%

B-MODT

B-MDQL4

A-MBA2

B-MDQSUB

B-MODT

A-MA9

A-MDML

A-MCKE

B-MCKB

B-MCKE

C1235

0.1uF

A-MODT

B-MDQL2

A-MA0

B-MDMU

B-MDQU4

A-MBA2

B-MA5

A-MDQL4

B-MBA2

B-MA11

B-MDQSL

A-MDQU0

R1232

10K

B-MDQL4

R1235

56

1%

B-MDML

A-MCK

C1231

0.1uF

A-MDQL6

A-MCKE

A-MDQSU

A-MCKB

A-MWEB

A-MA3

A-MDQL3

K4B1G1646G-BCK0

IC1201

DDR_1600_SS

EAN61836301

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

A13

T3

NC_5

M7

BA0

M2

BA1

N8

BA2

M3

CK

J7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J1

NC_2

J9

NC_3

L1

NC_4

L9

NC_6

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J2

VSS_6

J8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

C1210

0.1uF

C1247

1000pF

A-MCKB

A-MDQU4

A-MWEB

+1.5V_DDR

A-MA6

A-MA8

A-MRASB

B-MDQU6

A-MA5

B-MCKB

B-MA10

A-MDQSUB

A-MODT

A-MDQSL

A-MA13

B-MA2

B-MRESETB

A-MDQU3

R1238

56

1%

B-MA9

B-MA7

B-MA5

C1201

0.1uF

C1218

1uF

A-MDQSLB

B-MDQU2

B-MBA2

+1.5V_DDR

A-MA0

B-MA13

A-MDQU7

A-MVREFCA

C1216

0.1uF

R1201

1K

1%

C1229

0.1uF

B-MDQL5

B-MA2

B-MDQU5

R1236

56

1%

R1204

1K

1%

C1233

0.1uF

A-MVREFDQ

A-MDQL0

B-MA6

A-MDQU5

B-MA9

A-MA1

R1228

1K

1%

B-MA0

A-MA4

A-MRASB

B-MDQU3

A-MA12

B-MA0

B-MDQSU

B-MDQSLB

H5TQ2G63DFR-PBC

IC1202-*4

(OPT)(DDR_2G_1600_HYNIX)

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

A13

T3

NC_5

M7

BA0

M2

BA1

N8

BA2

M3

CK

J7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J1

NC_2

J9

NC_3

L1

NC_4

L9

NC_6

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J2

VSS_6

J8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

B-MDQU0

B-MA14

B-MA13

A-MDML

B-MVREFCA

A-MA10

A-MA10

+1.5V_DDR

R1203

240

1%

B-MDQSL

C1214

0.1uF

B-MDQU1

B-MVREFDQ

B-MBA0

A-MDQU6

C1232

0.1uF

B-MVREFDQ

B-MRESETB

A-MDMU

A-MDQL4

A-MA5

A-MDQL2

B-MVREFCA

A-MDQL3

B-MBA1

B-MA8

R1237

56

1%

B-MA1

B-MCASB

+1.5V_DDR

A-MDQU1

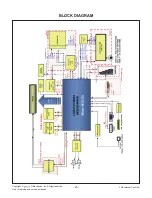

IC101

MSD804KKX

S7LR-M_NON_MS10(KR/US)

A_DDR3_A[0]

A11

A_DDR3_A[1]

C14

A_DDR3_A[2]

B11

A_DDR3_A[3]

F12

A_DDR3_A[4]

C15

A_DDR3_A[5]

E12

A_DDR3_A[6]

A14

A_DDR3_A[7]

D11

A_DDR3_A[8]

B14

A_DDR3_A[9]

D12

A_DDR3_A[10]

C16

A_DDR3_A[11]

C13

A_DDR3_A[12]

A15

A_DDR3_A[13]

E11

A_DDR3_A[14]

B13

A_DDR3_BA[0]

F13

A_DDR3_BA[1]

B15

A_DDR3_BA[2]

E13

A_DDR3_MCLK

C17

A_DDR3_MCLKZ

A17

A_DDR3_MCLKE

B16

A_DDR3_ODT

E14

A_DDR3_RASZ

B12

A_DDR3_CASZ

A12

A_DDR3_WEZ

C12

A_DDR3_RESET

F11

A_DDR3_DQSL

B19

A_DDR3_DQSLB

C18

A_DDR3_DQSU

B18

A_DDR3_DQSUB

A18

A_DDR3_DQML

E15

A_DDR3_DQMU

A21

A_DDR3_DQL[0]

D17

A_DDR3_DQL[1]

G15

A_DDR3_DQL[2]

B21

A_DDR3_DQL[3]

F15

A_DDR3_DQL[4]

B22

A_DDR3_DQL[5]

F14

A_DDR3_DQL[6]

A22

A_DDR3_DQL[7]

D15

A_DDR3_DQU[0]

G16

A_DDR3_DQU[1]

B20

A_DDR3_DQU[2]

F16

A_DDR3_DQU[3]

C21

A_DDR3_DQU[4]

E16

A_DDR3_DQU[5]

A20

A_DDR3_DQU[6]

D16

A_DDR3_DQU[7]

C20

B_DDR3_A[0]

B23

B_DDR3_A[1]

D25

B_DDR3_A[2]

F22

B_DDR3_A[3]

G22

B_DDR3_A[4]

E24

B_DDR3_A[5]

F21

B_DDR3_A[6]

E23

B_DDR3_A[7]

D22

B_DDR3_A[8]

D24

B_DDR3_A[9]

D21

B_DDR3_A[10]

C24

B_DDR3_A[11]

C25

B_DDR3_A[12]

F23

B_DDR3_A[13]

E21

B_DDR3_A[14]

D23

B_DDR3_BA[0]

G20

B_DDR3_BA[1]

F24

B_DDR3_BA[2]

F20

B_DDR3_MCLK

G25

B_DDR3_MCLKZ

G23

B_DDR3_MCLKE

F25

B_DDR3_ODT

D20

B_DDR3_RASZ

B25

B_DDR3_CASZ

B24

B_DDR3_WEZ

A24

B_DDR3_RESET

E20

B_DDR3_DQSL

K24

B_DDR3_DQSLB

K25

B_DDR3_DQSU

J21

B_DDR3_DQSUB

J20

B_DDR3_DQML

H24

B_DDR3_DQMU

L20

B_DDR3_DQL[0]

L23

B_DDR3_DQL[1]

J24

B_DDR3_DQL[2]

L24

B_DDR3_DQL[3]

J23

B_DDR3_DQL[4]

M24

B_DDR3_DQL[5]

H23

B_DDR3_DQL[6]

M23

B_DDR3_DQL[7]

K23

B_DDR3_DQU[0]

G21

B_DDR3_DQU[1]

L22

B_DDR3_DQU[2]

H22

B_DDR3_DQU[3]

K20

B_DDR3_DQU[4]

H20

B_DDR3_DQU[5]

L21

B_DDR3_DQU[6]

H21

B_DDR3_DQU[7]

K21

B-MA1

R1226

240

1%

A-MRESETB

R1231

10K

B-MCK

A-MDQSUB

A-MCASB

A-MDQU5

B-MDQL3

A-MDQU4

C1213

0.1uF

A-MDQL6

B-MDQU2

B-MDQU0

B-MDQSUB

A-MDMU

C1249

1000pF

A-MDQU3

B-MA12

A-MDQSL

B-MA4

C1207

0.1uF

A-MVREFCA

B-MRASB

B-MDQU1

A-MCASB

B-MDMU

B-MA4

A-MA6

C1208

0.1uF

C1234

0.1uF

C1203

0.1uF

A-MDQU7

B-MCASB

C1202

1000pF

B-MDQL7

C1239

0.1uF

R1202

1K

1%

C1204

1000pF

B-MDQL6

A-MDQU6

B-MA14

+1.5V_DDR

B-MDML

B-MDQL0

A-MA7

C1248

0.1uF

C1212

0.1uF

K4B1G1646G-BCK0

IC1202

DDR_1600_SS

EAN61836301

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

A13

T3

NC_5

M7

BA0

M2

BA1

N8

BA2

M3

CK

J7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J1

NC_2

J9

NC_3

L1

NC_4

L9

NC_6

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J2

VSS_6

J8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

K4B2G1646E-BCK0

IC1201-*5

BR/ASIA(DDR_2G_1600_SS)

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

A13

T3

NC_5

M7

BA0

M2

BA1

N8

BA2

M3

CK

J7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J1

NC_2

J9

NC_3

L1

NC_4

L9

NC_6

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J2

VSS_6

J8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

A-MBA1

B-MA7

B-MA3

A-MDQL2

B-MCK

A-MDQSLB

A-MDQL1

A-MA14

A-MA4

H5TQ1G63EFR-PBC

IC1202-*1

DDR_1600_HYNIX_9003(DEV)

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

NC_7

T3

NC_5

M7

BA0

M2

BA1

N8

BA2

M3

CK

J7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J1

NC_2

J9

NC_3

L1

NC_4

L9

NC_6

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J2

VSS_6

J8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

B-MDQU7

C1205

10uF

A-MDQU2

C1206

0.1uF

C1251

10uF

A-MBA0

R1224

1K

1%

C1241

1uF

C1238

1uF

A-MDQL5

A-MA2

C1209

0.01uF

25V

C1240

0.01uF

25V

NC4_S7LRM

CLose to Saturn7M IC

2G 1600

1G 1600

CLose to Saturn7M IC

CLose to DDR3

CLose to DDR3

2013.05.06

EAX65374701_29"_Brazil

Copyright ⓒ 2013 LG Electronics. Inc. All right reserved.

Only for training and service purposes

LGE Internal Use Only

Содержание 29LN300B

Страница 33: ......