XC800 Debugger | 9

©

1989-2021

Lauterbach GmbH

Configuration

The processor type must be selected by the

SYStem.CPU

command before issuing any other target related

commands.

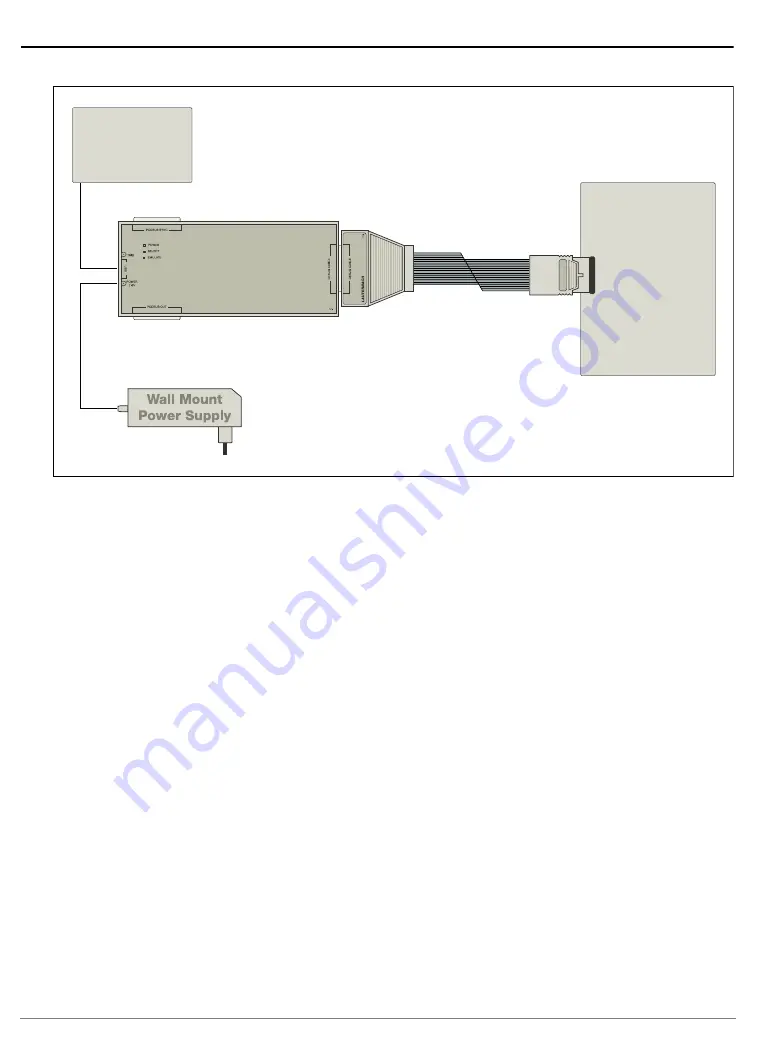

POWER DEBUG USB INTERFACE / USB 3

POWER DEBUG INTERFACE / USB 3

PC or

Workstation

USB

Cable

Target

Deb

ug

Connector

Debug Cable