XV-LTR1

1-30

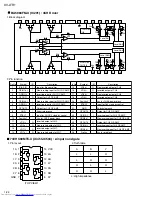

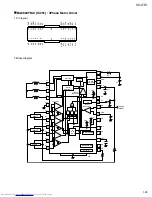

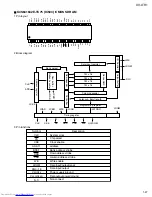

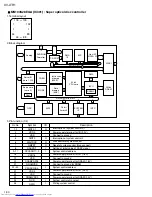

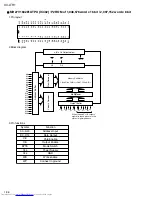

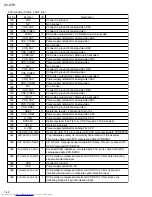

MN103S28EGA (IC301) : Super optical disc controller

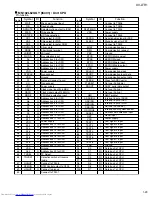

1.Terminal layout

2.Block diagram

DVD-ROM

Formatter

CGEN

CD-PRE

Instruction

memory

(40KB)

DMA

I/F

ECC

Host I/F

MPEG I/F

High speed IO bus

32 bit

CPU core

DMA

Data

memory

(6KB)

BCU

DRAMC

ATAPI

2Mbit

DRAM

INTC

SYSTEM

I/F

16 bit

timer x 2

WDT

CIRC

General purpose IO bus

MODE

Servo I/O

(core 1 I/O)

Analog

Servo core

(core 2)

RAM

1

44

132

89

176 133

45 88

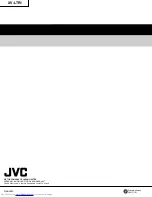

1,2

3

4

5

6

7

8

9~17

18

19

20

21

22~30

31

32

33

34

35

O

-

-

O

O

O

I

I

-

-

-

-

I

-

-

-

I

I

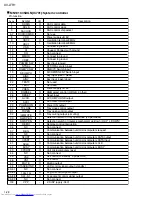

Pin No.

Symbol

NINT0,1

VDD3

VSS

NINT2

WAITDOC

NMPST

DASPST

CPUADR17~9

VDD18

VSS

DRAMVDD18

DRAMVSS

CPUADR8~0

VDD3

VSS

DRAMVDD3

NCS

NWR

I/O

Description

3.Pin function (1/4)

Interruption of system control 0,1

Power supply terminal for I/O(3.3V)

Connect to ground

Interruption of system control 2

Wait control of system control

Reset of system control (Non connect)

Setting of initial value of DASP signal

System control address

Power supply terminal for I/O (1.8V)

Connect to ground

Power supply terminal for DRAM (1.8V)

Connect to ground for DRAM

System control address

Power supply terminal for I/O (3.3V)

Connect to ground

Power supply terminal for DRAM (3.3V)

System control chip select

Writing system control