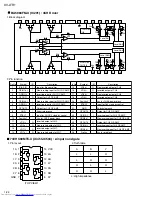

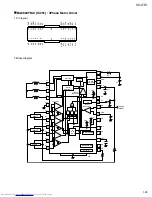

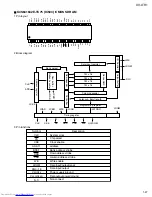

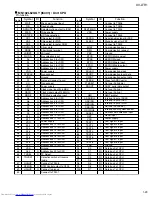

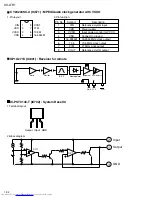

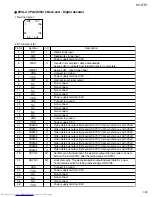

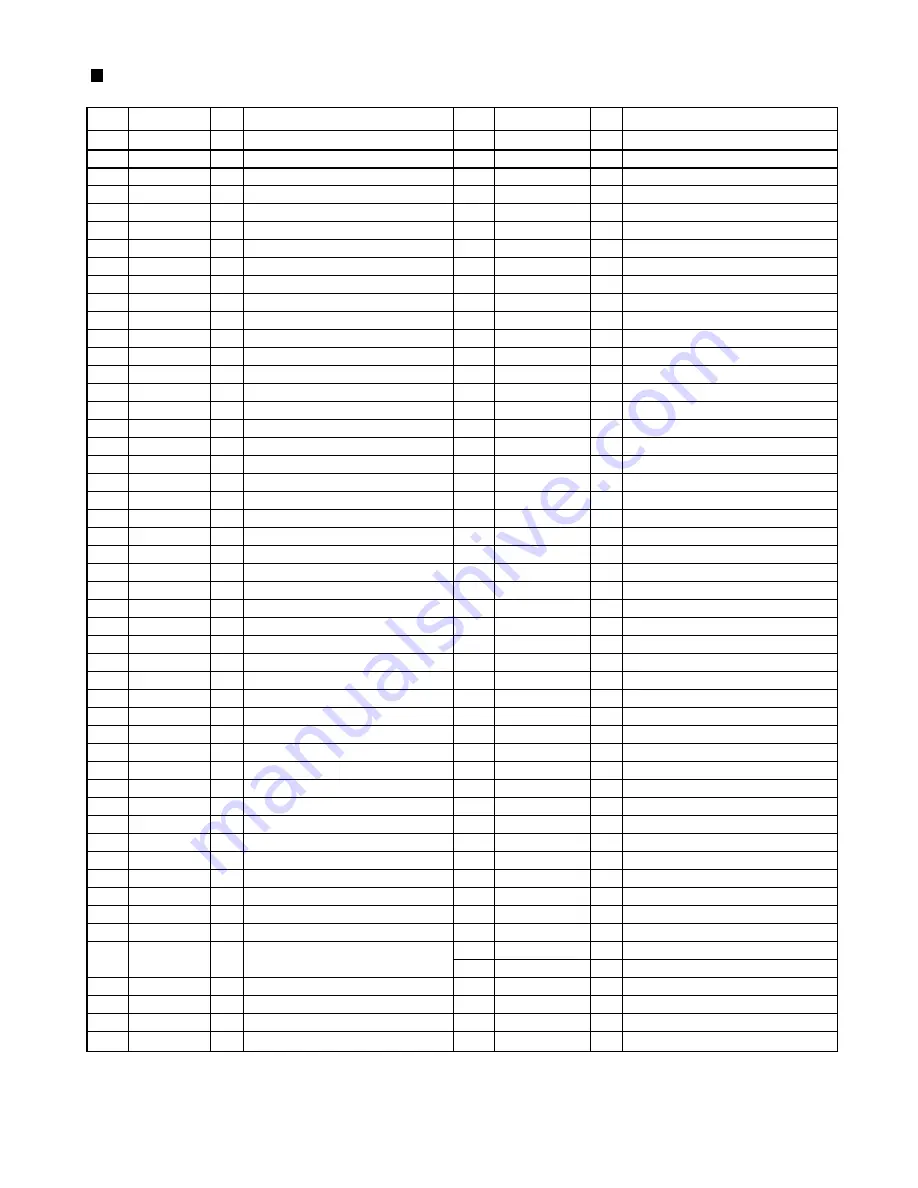

XV-LTR1

1-29

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

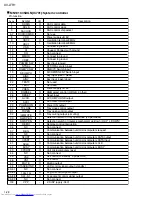

WAIT

RE

SPMUTE

WEN

HDTYPE

CS1

CS2

CS3

DRVMUTE

SBRK

LSIRST

WORD

A0

A1

A2

A3

VDD

SYSCLK

VSS

XI

XO

VDD

OSCI

OSCO

MODE

A4

A5

A6

A7

A8

A9

A10

A11

VDD

A12

A13

A14

A15

A16

A17

A18

A19

VSS

A20

TXSEL

TRVSW

HUGUP

HFMON

HAGUP

-

Micon wait signal input

Read enable

Spindle muting output to IC251

Write enable

HD Type selection

Chip select for ODC

Chip select for ZIVA

Chip select for outer ROM

Driver mute

Short brake terminal

LSI reset

Bus selection input

Address bus 0 for CPU

Address bus 1 for CPU

Address bus 2 for CPU

Address bus 3 for CPU

Power supply

Non connect

Ground

Not use (Connect to vss)

Non connect

Power supply

Clock signal input(13.5MHz)

Clock signal output(13.5MHz)

CPU Mode selection input

Address bus 4 for CPU

Address bus 5 for CPU

Address bus 6 for CPU

Address bus 7 for CPU

Address bus 8 for CPU

Address bus 9 for CPU

Address bus 10 for CPU

Address bus 11 for CPU

Power supply

Address bus 12 for CPU

Address bus 13 for CPU

Address bus 14 for CPU

Address bus 15 for CPU

Address bus 16 for CPU

Address bus 17 for CPU

Address bus 18 for CPU

Address bus 19 for CPU

Ground

Address bus 20 for CPU

TX Select

Detection switch of traverse

inside

Connect to TP408

HFM Control output to Q103

Connect to pick-up

Connect to TP407

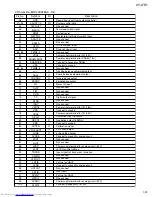

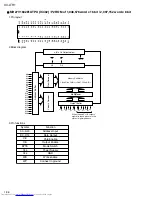

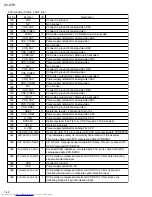

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

-

-

P85/TM5IO

VDD

-

FEPEN

SLEEP

-

BUSY

REQ

VSS

EPCS

EPSK

EPDI

EPDO

VDD

SCLKO

S2UDT

U2SDT

CPSCK

P74/SBI1

SDOUT

-

-

NMI

ADSCIRQ

ODCIRQ

DECIRQ

CSSIRQ

ODCIRQ2

ADSEP

RST

VDD

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

TEST7

TEST8

VSS

D0

D1

D2

D3

D4

D5

D6

D7

Connect to TP406

Connect to TP405

Connect to TP404

Power supply

Connect to TP403

Serial enable signal for FEP

Standby signal for FEP

Connect to TP402

Communication busy

Communication request

Ground

EEPROM chip select

EEPROM clock

EEPROM data input

EEPROM data output

Power supply

Communication clock

Communication input data

Communication output data

Clock for ADSC serial

Not use (Pull down)

ADSC serial data output

Not use (Pull up)

Not use (Pull up)

NMI Terminal

Interrupt input of ADSC

Interrupt input of ODC

Interrupt input of ZIVA

Not use (Pull down)

Interruption of system control

Address data selection input

Reset input

Power supply

Test signal 1 input

Test signal 2 input

Test signal 3 input

Test signal 4 input

Test signal 5 input

Test signal 6 input

Test signal 7 input

Test signal 8 input

Ground

Data bus 0 of CPU

Data bus 1 of CPU

Data bus 2 of CPU

Data bus 3 of CPU

Data bus 4 of CPU

Data bus 5 of CPU

Data bus 6 of CPU

Data bus 7 of CPU

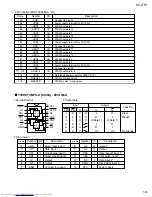

I

O

O

O

O

O

O

O

O

O

O

I

O

O

O

O

-

-

-

-

-

-

I

O

I

O

O

O

O

O

O

O

O

-

O

O

O

O

O

O

O

O

-

O

O

I

-

O

O

-

-

-

-

-

-

O

O

-

I

O

-

O

O

I

O

-

O

I

O

O

I

O

I

I

I

I

I

I

I

I

I

I

-

I

I

I

I

I

I

I

I

-

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Pin No.

Pin No.

Symbol

Symbol

I/O

I/O

Function

Function

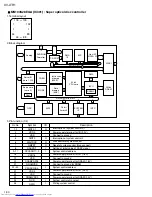

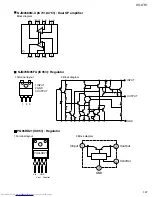

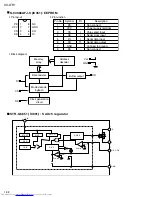

MN102L62GGY (IC401) : Unit CPU

Pin function