(No.YA707<Rev.001>)2-81

2-82(No.YA707<Rev.001>)

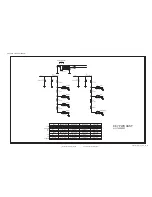

MAIN PWB ASS'Y(37/46)

[STi7103 DEBUG PORT and RESET S/W]

HU-71100006

hb1_main_0612_38/48_0.0

1

1

2

2

3

3

4

4

5

5

6

6

A

A

B

B

C

C

D

D

ST_RESET

+5V

+5V

ST_3V3

ST_3V3

ST_3V3

+3V3_STI7103

+5V

+3V3_STI7103

DCU_nRESET

RS232_TXD3

RS232_RXD3

ST_RESET

STb7100_nRESET

M_RST_N

DEBUG PORT 1

JTAG Open drain output

All location are from 1361 to 1380

JP1362

OPEN-HEADER 2P

1

2

R1376

103/1005

R1370

472/1005

R1374

472/1005

Q1366

OPEN-MMBT4401

1

23

Q1364

MMBT4401

1

23

C1365

104p/16V/1005

Q1362

MMBT4401

1

23

R1364

332/1005

Q1361

MMBT4401

1

23

R1363

332/1005

R1362

103/1005

R1373

331/1005

R1372

103/1005

R1367

473/1005

R1367

473/1005

Q1365

FDV301N_NL

Q1369

FDV301N_NL

1

3

2

1

3

2

R1361

472/1005

R1375

OPEN-102/1005

C1366

104p/16V/1005

R1368

472/1005

R1365

472/1005

R1371

103/1005

S1361

OPEN-JTP1127WEM

1

2

3

4

Q1363

MMBT4401

1

23

2mm

JP1361

OPEN-53014-0410

4

3

2

1

MAIN PWB(36/46)

MAIN PWB(7/46)

MAIN PWB(5/46)

MAIN PWB(31/46)

MAIN PWB(31/46)

MAIN PWB CIRCUIT DIAGRAM (37/46) [STi7103 DEBUG PORT and RESET S/W]