2-8(No.YA707<Rev.001>)

(No.YA707<Rev.001>)2-7

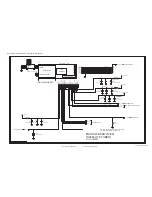

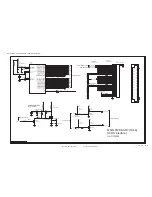

TX

RX

R

CLK/BLANK/HSYNC/VSYNC

DVO[0..23]

I2S / SPDIF

I2S / SPDIF

VXI

CONT

DATA

UART1

CVBS

ROM MEM

CTL. BUS

POD_CTL.

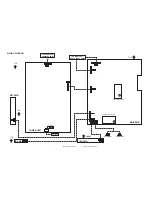

STI7103 System DDR memory

EMI ADDR[1:23]

/EMI DATA[0:15]

NOR FLASH

PC28F320J3D75/BGA

(32Mbit(4Mx8))

Douglas DEMO B/D 256Mbit

SLMI DDRA[0:12]

/SLMI DDRDQ[0:31]

EMI ADDR[1:23]

/EMI DATA[0:15]

CIO TS

Cl contro

I2S / SPDIF

DVO

CONT

DATA

UART1

CVBS

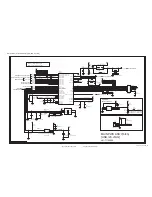

RF_IN1

SIF

RF_CVBS

TUNER0_I2C

/-

DEV_/RESET

TUNER0_I2C

DEV_/RESET

/-

TUNER1_I2C

LNB_OUT

RF_IN1

FLI_I2C0

TS0

TS

TS

TS_SEL0

FLI_I2C0

DEV_/RESET

FLI_I2C0

nTS_SEL0

22K_TONE

U961

DEMOD

U921 TERRESTRIAL TUNER

U1021 SATELLITE TUNER

U51

BCM4506

U1051

A8293(LNB)

CII TS

POD_DET

nTS_SEL1

TS Selector

MUX TS

TS_SEL1

DTT_CVBS

U102

SCALER

U1131

MPEG CPU

JP221

CI SLOT

Buffer&SW

HOST_A[1:2]/HOST_D[0:7]

POD_CTL

POD_DET

TSIN0

DTT_CVBS

TS_Parallel

[POD]

Inputs

FLI_I2C0

I2C0

GP0132

TS_SEL0

TS_SEL1

UD1261, UD1262

DDR SDRAM

BLOCK DIAGRAM [MPEG4 BLOCK]