User’s Manual

291

B.1.7 RAM Segment Relocation

Normally when instruction/data separation is enabled, instructions are stored in flash

memory and data are stored in RAM memory. This can present a problem for the Interrupt

Service Routine area, which often requires run-time modification. The RAM Segment

Register (RAMSR) allows a 1, 2, or 4 KB segment of the logical memory space to be

mapped as data would be mapped, even for program execution.

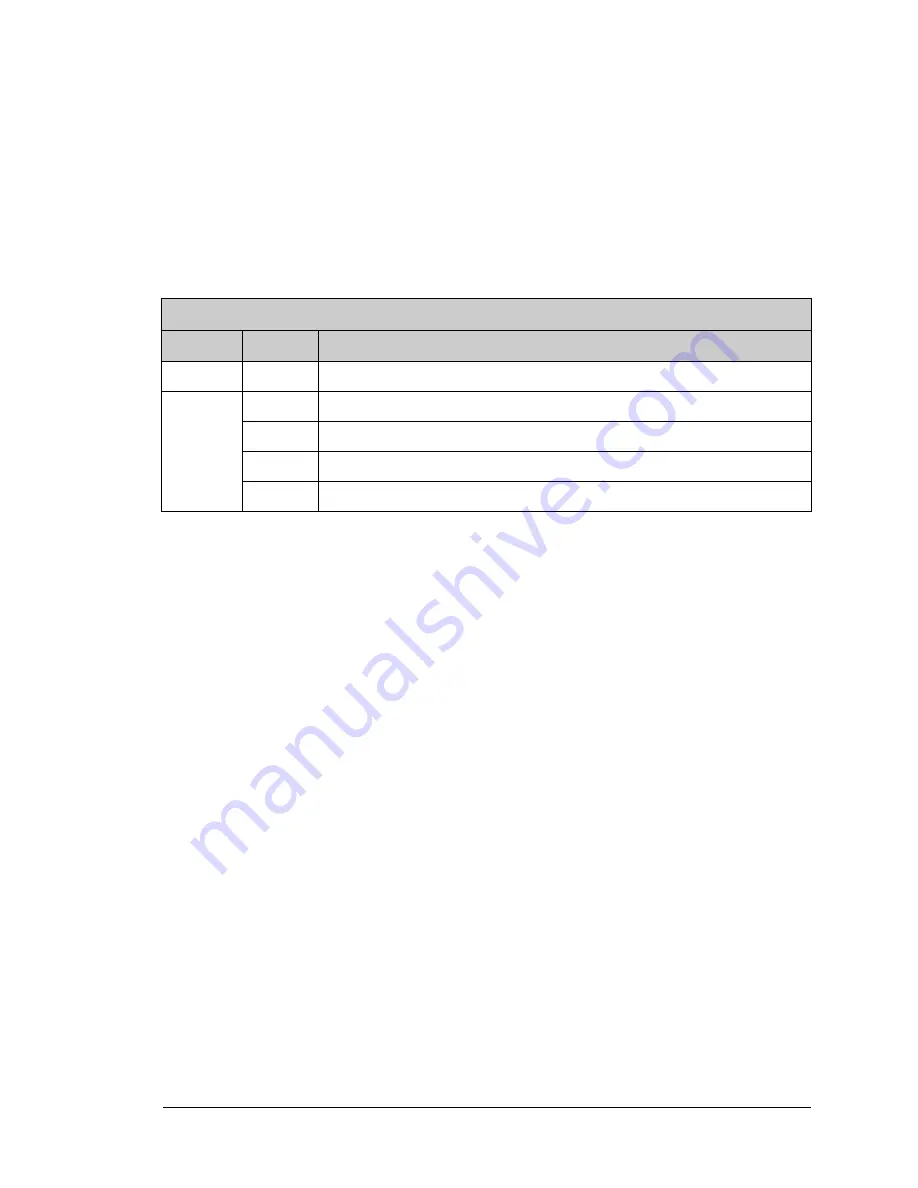

Table B-15. RAM Segment Register

RAM Segment Register (RAMSR) (Address = 0x0448)

Bit(s)

Value

Description

7:2

Compare value for RAM segment limit checking.

1:0

00

Disable RAM segment limit checking.

01

Select data-type MMU translation if PC[15:10] is equal to RAMSR[7:2].

10

Select data-type MMU translation if PC[15:11] is equal to RAMSR[7:3].

11

Select data-type MMU translation if PC[15:12] is equal to RAMSR[7:4].

Содержание Rabbit 2000

Страница 2: ...Rabbit 3000 Microprocessor User s Manual 019 0108 040731 O ...

Страница 9: ...Rabbit 3000 Microprocessor ...

Страница 29: ...20 Rabbit 3000 Microprocessor ...

Страница 64: ...User s Manual 55 5 PIN ASSIGNMENTS AND FUNCTIONS ...

Страница 79: ...70 Rabbit 3000 Microprocessor ...

Страница 80: ...User s Manual 71 6 RABBIT INTERNAL I O REGISTERS ...

Страница 123: ...114 Rabbit 3000 Microprocessor ...

Страница 137: ...128 Rabbit 3000 Microprocessor ...

Страница 157: ...148 Rabbit 3000 Microprocessor ...

Страница 207: ...198 Rabbit 3000 Microprocessor ...

Страница 249: ...240 Rabbit 3000 Microprocessor ...

Страница 255: ...246 Rabbit 3000 Microprocessor ...

Страница 277: ...268 Rabbit 3000 Microprocessor ...

Страница 343: ...334 Rabbit 3000 Microprocessor ...

Страница 345: ......