Developer’s Manual

January, 2004

97

Intel XScale® Core

Developer’s Manual

Configuration

7.3.1.2

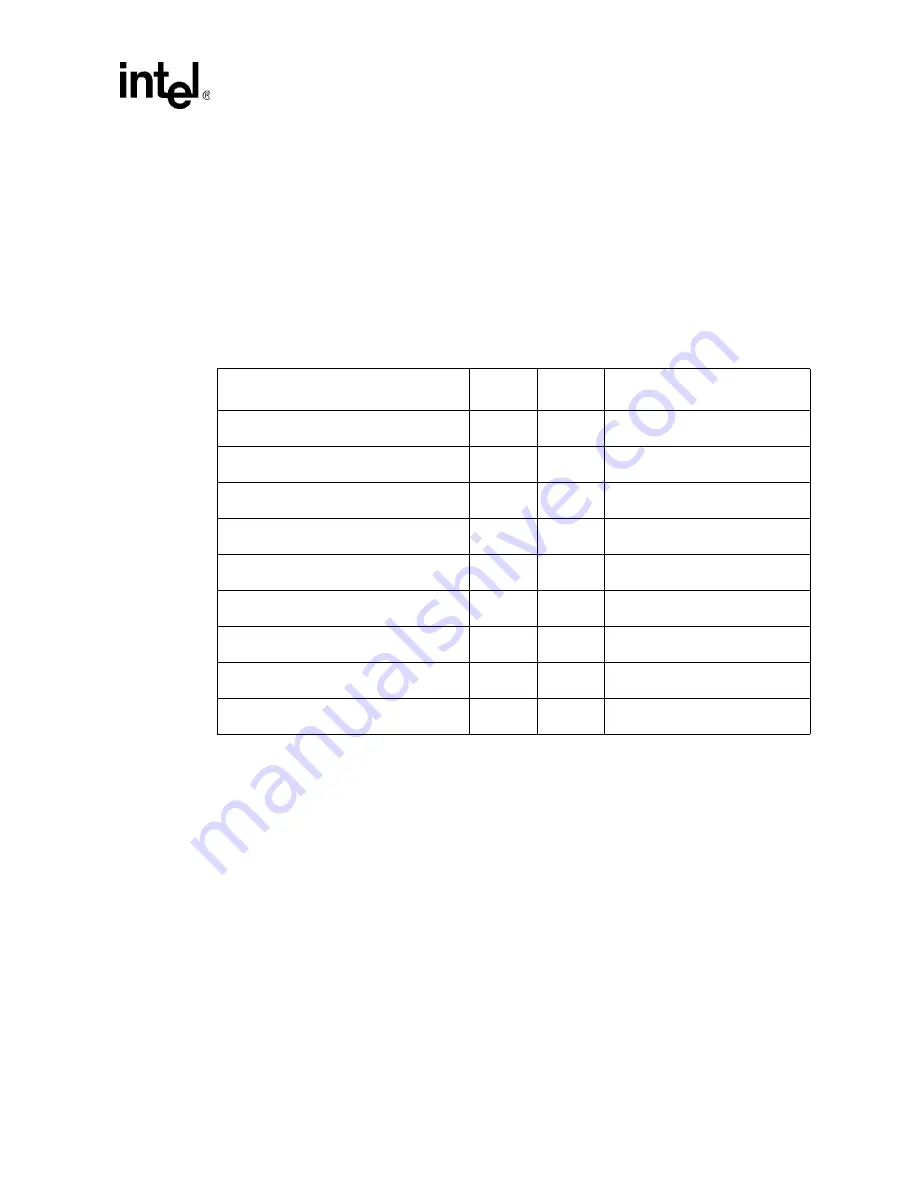

XSC2 Performance Monitoring Registers

The performance monitoring unit in XSC2 contains a control register (PMNC), a clock counter

(CCNT), interrupt enable register (INTEN), overflow flag register (FLAG), event selection register

(EVTSEL) and four event counters (PMN0 through PMN3). The format of these registers can be

found in

Chapter 8, “Performance Monitoring”

, along with a description on how to use the

performance monitoring facility.

Opcode_2 should be zero on all accesses.

These registers can’t be accessed by LDC and STC coprocessor instructions.

Table 7-22.

Accessing the XSC2 Performance Monitoring Registers

Description

CRn

Register#

CRm

Register#

Instruction

(PMNC) Performance Monitor Control

Register

0b0000

0b0001

Read: MRC p14, 0, Rd, c0, c1, 0

Write: MCR p14, 0, Rd, c0, c1, 0

(CCNT) Clock Counter Register

0b0001

0b0001

Read: MRC p14, 0, Rd, c1, c1, 0

Write: MCR p14, 0, Rd, c1, c1, 0

(INTEN) Interrupt Enable Register

0b0100

0b0001

Read: MRC p14, 0, Rd, c4, c1, 0

Write: MCR p14, 0, Rd, c4, c1, 0

(FLAG) Overflow Flag Register

0b0101

0b0001

Read: MRC p14, 0, Rd, c5, c1, 0

Write: MCR p14, 0, Rd, c5, c1, 0

(EVTSEL) Event Selection Register

0b1000

0b0001

Read: MRC p14, 0, Rd, c8, c1, 0

Write: MCR p14, 0, Rd, c8, c1, 0

(PMN0) Performance Count Register 0

0b0000

0b0010

Read: MRC p14, 0, Rd, c0, c2, 0

Write: MCR p14, 0, Rd, c0, c2, 0

(PMN1) Performance Count Register 1

0b0001

0b0010

Read: MRC p14, 0, Rd, c1, c2, 0

Write: MCR p14, 0, Rd, c1, c2, 0

(PMN2) Performance Count Register 2

0b0010

0b0010

Read: MRC p14, 0, Rd, c2, c2, 0

Write: MCR p14, 0, Rd, c2, c2, 0

(PMN3) Performance Count Register 3

0b0011

0b0010

Read: MRC p14, 0, Rd, c3, c2, 0

Write: MCR p14, 0, Rd, c3, c2, 0