Developer’s Manual

January, 2004

171

Intel XScale® Core

Developer’s Manual

Performance Considerations

10.4.7

Load/Store Instructions

10.4.8

Semaphore Instructions

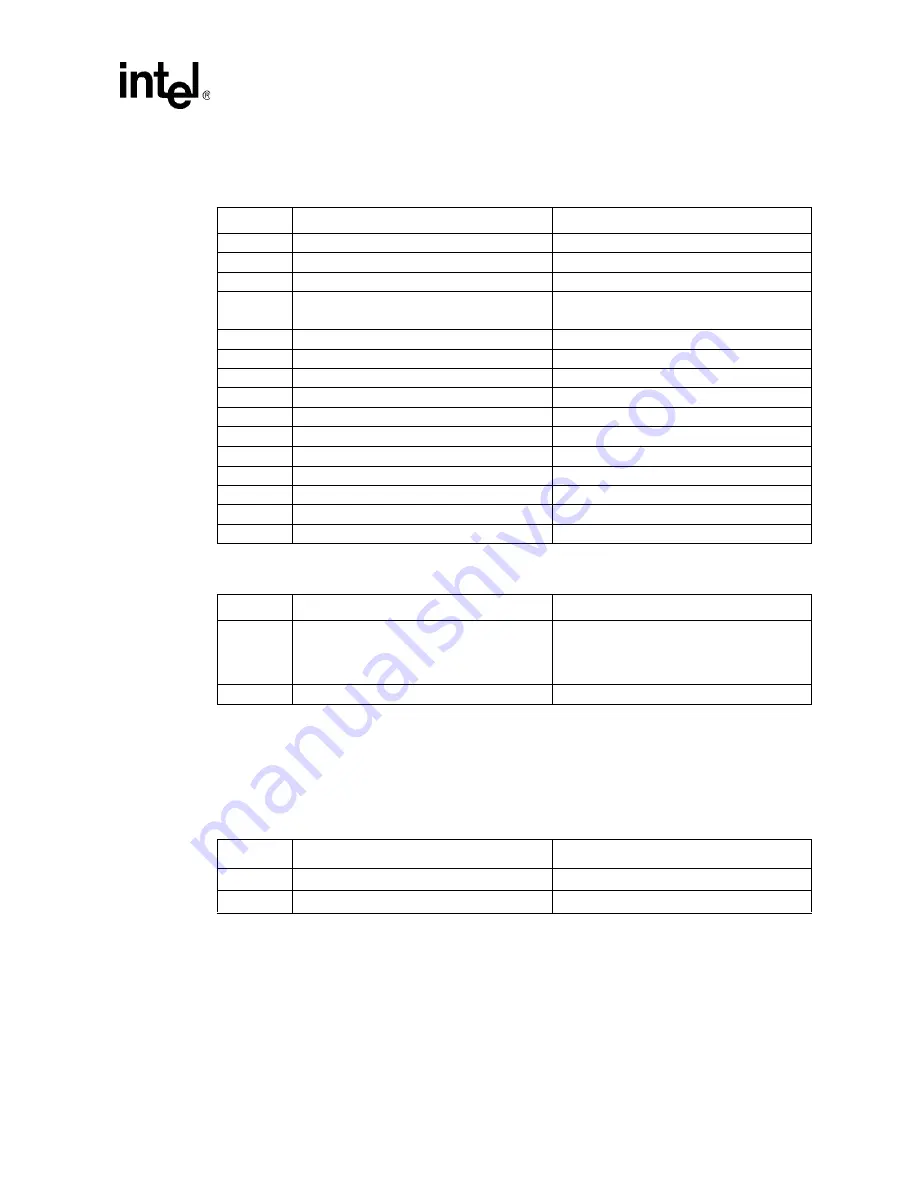

Table 10-11. Load and Store Instruction Timings

Mnemonic

Minimum Issue Latency

Minimum Result Latency

LDR

1

3 for load data; 1 for writeback of base

LDRB

1

3 for load data; 1 for writeback of base

LDRBT

1

3 for load data; 1 for writeback of base

LDRD

1 (+1 if Rd is R12)

3 for Rd; 4 for Rd+1;

1 (+1 if Rd is R12) for writeback of base

LDRH

1

3 for load data; 1 for writeback of base

LDRSB

1

3 for load data; 1 for writeback of base

LDRSH

1

3 for load data; 1 for writeback of base

LDRT

1

3 for load data; 1 for writeback of base

PLD

1

N/A

STR

1

1 for writeback of base

STRB

1

1 for writeback of base

STRBT

1

1 for writeback of base

STRD

2

2 for writeback of base

STRH

1

1 for writeback of base

STRT

1

1 for writeback of base

Table 10-12. Load and Store Multiple Instruction Timings

Mnemonic

Minimum Issue Latency

Minimum Result Latency

LDM

a

a.

See

Table 10-4

for LDM timings when R15 is in the register list

2 + numreg

b

b.

numreg is the number of registers in the register list

5-18 for load data (4 + numreg for last register

in list; 3 + numreg for 2nd to last register in list;

2 + numreg for all other registers in list);

2+ numreg for writeback of base

STM

2 + numreg

2 + numreg for writeback of base

Table 10-13. Semaphore Instruction Timings

Mnemonic

Minimum Issue Latency

Minimum Result Latency

SWP

5

5

SWPB

5

5