114

January, 2004

Developer’s Manual

Intel XScale® Core

Developer’s Manual

Performance Monitoring

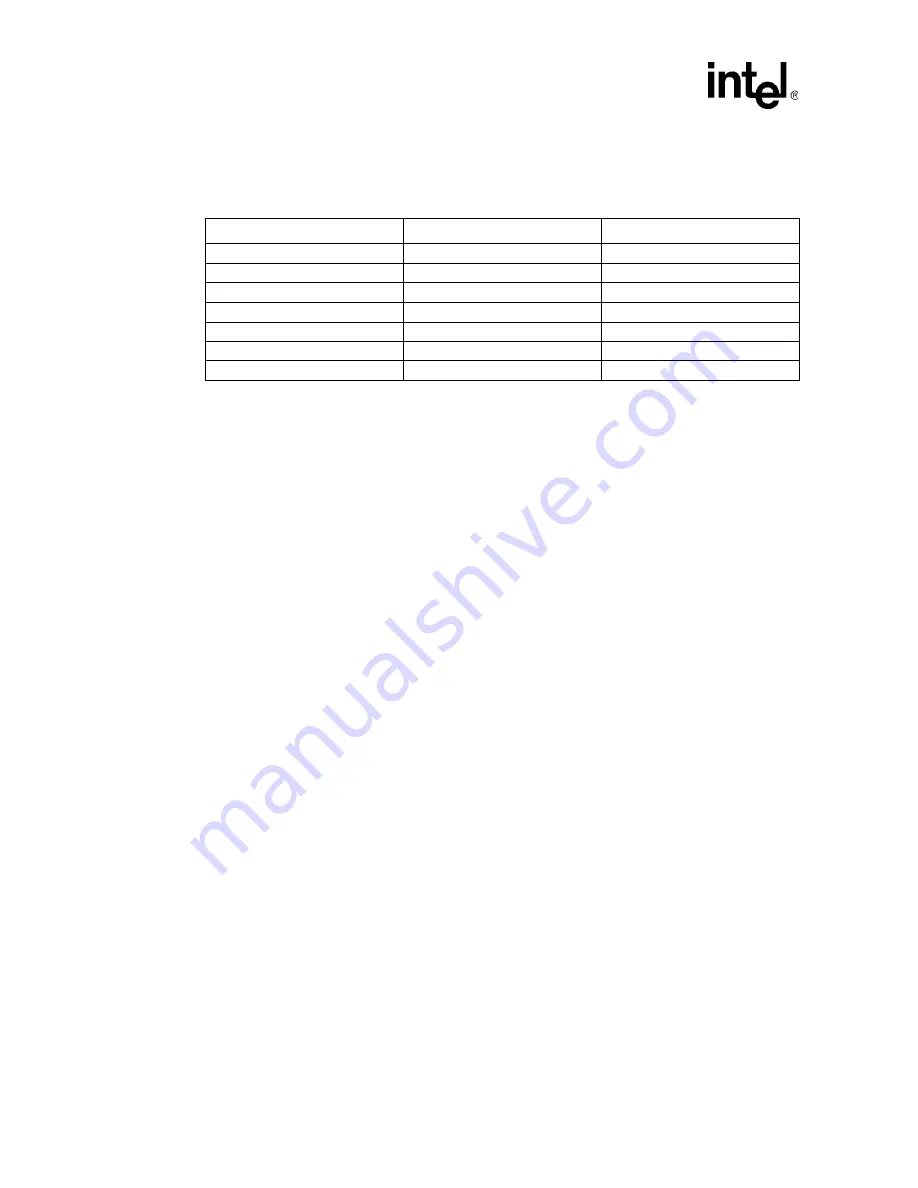

Some typical combinations of counted events are listed in this section and summarized in

Table 8-13

. In this section, we call such an event combination a mode.

Note:

PMN0 and PMN1 were used for illustration purposes only. Given there are four event counters,

more elaborate combination of events could be constructed. For example, one performance run

could select 0xA, 0xB, 0xC, 0x9 events from which data cache performance statistics could be

gathered (like hit rates, number of writebacks per data cache miss, and number of times the data

cache buffers fill up per request).

Table 8-13.

Some Common Uses of the PMU

Mode

evtCount0

evtCount1

Instruction Cache Efficiency

0x7 (instruction count)

0x0 (ICache miss)

Data Cache Efficiency

0xA (Dcache access)

0xB (DCache miss)

Instruction Fetch Latency

0x1 (ICache cannot deliver)

0x0 (ICache miss)

Data/Bus Request Buffer Full

0x8 (DBuffer stall duration)

0x9 (DBuffer stall)

Stall/Writeback Statistics

0x2 (data stall)

0xC (DCache writeback)

Instruction TLB Efficiency

0x7 (instruction count)

0x3 (ITLB miss)

Data TLB Efficiency

0xA (Dcache access)

0x4 (DTLB miss)