Boxed Processor Specifications

108

Datasheet

NOTES:

1.

Set point variance is approximately ± 1

°

C from fan heatsink to fan heatsink.

If the boxed processor fan heatsink 4-pin connector is connected to a 4-pin

motherboard header and the motherboard is designed with a fan speed controller with

PWM output (CONTROL see

) and remote thermal diode measurement

capability the boxed processor will operate as follows:

As processor power has increased the required thermal solutions have generated

increasingly more noise. Intel has added an option to the boxed processor that allows

system integrators to have a quieter system in the most common usage.

The 4th wire PWM solution provides better control over chassis acoustics. This is

achieved by more accurate measurement of processor die temperature through the

processor's temperature diode (T-diode). Fan RPM is modulated through the use of an

ASIC located on the motherboard that sends out a PWM control signal to the 4th pin

of the connector labeled as CONTROL. The fan speed is based on actual processor

temperature instead of internal ambient chassis temperatures.

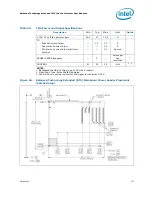

Figure 39.

Boxed Processor Fan Heatsink Set Points

Table 39.

Fan Heatsink Power and Signal Specifications

Boxed Processor Fan

Heatsink Set Point (°C)

Boxed Processor Fan Speed

Notes

X

≤

30

When the internal chassis temperature is below or equal to

this set point, the fan operates at its lowest speed.

Recommended maximum internal chassis temperature for

nominal operating environment.

1

Y = 35

When the internal chassis temperature is at this point, the

fan operates between its lowest and highest speeds.

Recommended maximum internal chassis temperature for

worst-case operating environment.

-

Z

≥

38

When the internal chassis temperature is above or equal to

this set point, the fan operates at its highest speed.

-

Lower Set Point

Lowest Noise Level

Internal Chassis Temperature (Degrees C)

X

Y

Z

Increasing Fan

Speed & Noise

Higher Set Point

Highest Noise Level

Содержание CORE 2 DUO E4000 - 3-2008

Страница 8: ...8 Datasheet ...

Страница 10: ...10 Datasheet ...

Страница 36: ...Electrical Specifications 36 Datasheet ...

Страница 38: ...Package Mechanical Specifications 38 Datasheet Figure 9 Processor Package Drawing Sheet 1 of 3 ...

Страница 39: ...Datasheet 39 Package Mechanical Specifications Figure 10 Processor Package Drawing Sheet 2 of 3 ...

Страница 40: ...Package Mechanical Specifications 40 Datasheet Figure 11 Processor Package Drawing Sheet 3 of 3 ...

Страница 46: ...Package Mechanical Specifications 46 Datasheet ...

Страница 100: ...Features 100 Datasheet ...

Страница 110: ...Boxed Processor Specifications 110 Datasheet ...

Страница 122: ...Debug Tools Specifications 122 Datasheet ...