3-4 OTHER CIRCUITS

• REPEATER CONTROL CIRCUITS (MAIN UNIT)

The repeater control circuits consist of the CPU (IC5), Boot

ROM (IC12), Flash ROM (IC11), SRAM (IC2, IC3, IC6, IC7).

A 32-bit processor is adopted as the CPU (IC5), and the 22

MHz signal, generated by the clock oscillator (X2), is used

for the CPU clock after being multiplied by 6 at the inside

the CPU.

The Boot ROM (IC12) is 16 M-bit flash memory as 8 bits

each.

The Flash ROM (IC11) is 32 M-bit flash memory as 16 bits

each.

The SRAM circuit (IC2, IC3, IC6, IC7) contains four 4 M-bit

SRAM IC as 32 bits each.

• 33 MHz CLOCK CIRCUIT (MAIN UNIT)

The 22 MHz clock signal is multiplied by

3

/

2

at the inside of

the CPU (IC5) and then amplified at the clock driver (IC15).

The amplified clock signal is applied to the PCI/DMA FPGA

IC (IC15), Ethernet controller (IC8), ATM-SAR controller

(IC16).

• USB CONTROLLER (MAIN UNIT)

While setting the ASSIST repeater (ID-RP2L), the USB con-

trollers are used for communication with the connected PC.

While reading the setting data from the connected ASSIST

repeater (ID-RP2L), the setting data is applied to the LVDS

receivers (IC25, IC26) in the differential data format. The

applied data format is converted into the serial data format

at the LVDS receivers (IC25, IC26).

The converted serial data is applied to the USB controllers

(IC27, IC28) to be converted into the USB data format. The

converted USB data is applied to the connected PC via

[SERVICE 1] (J19) or [SERVICE 2] (J20) connector.

While writing the setting data to the connected ASSIST

repeater (ID-RP2L), the setting data is applied to the USB

controllers (IC25, IC26) via [SERVICE 1] (J19) or [SERVICE

2] (J20) connector. The USB controllers (IC25, IC26) con-

vert the applied data format into the serial data format.

The converted serial data is applied to the LVDS driver (IC22)

and converted into the differential data format. The con-

verted differential data is applied to the connected ASSIST

repeater (ID-RP2L).

B - 3 - 2

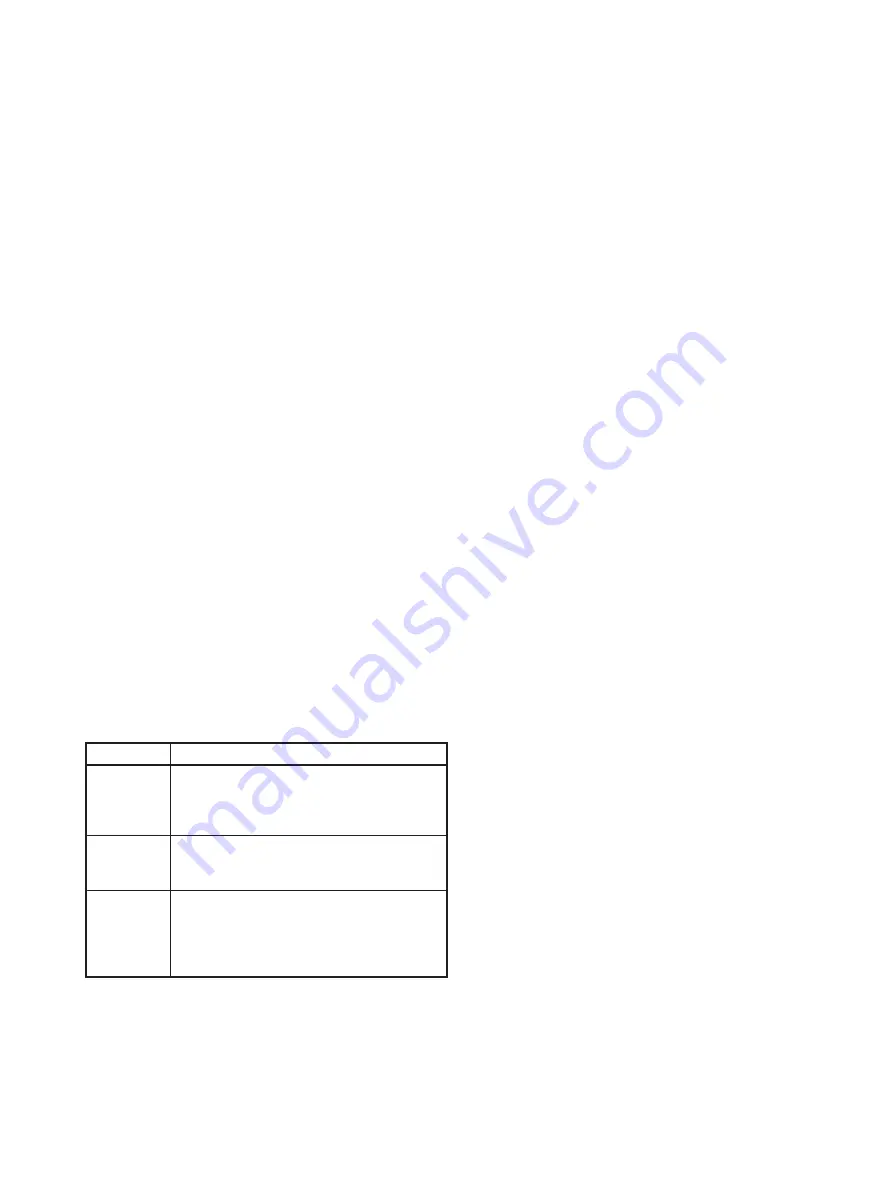

3-3 POWER SUPPLY CIRCUITS

Line

Description

3.3 V

Common 3.3 V converted from the 13.8 V

line by the 3.3 V regulator circuit (IC13). The

output voltage is applied to the SRAM ICs (IC2,

IC3, IC6, IC7), ATM-SAR controller (IC16), etc.

1 . 8 V

Common 1.8 V converted from the 3.3 V

line by the 1.8 V regulator circuit (IC33). The

output voltage is applied to the CPU (IC5).

1.5 V

Common 1.5 V converted from the 3.3 V

line by the 1.5 V regulator circuit (IC34). The

output voltage is applied to the ASSIST IF

FPGA IC (IC19), LOCAL RPT I/F FPGA IC

(IC24), etc.

3-2-2 DURING ASSIST REPEATER OPERATION

(MAIN UNIT)

The data signal from the PCI/DMA FPGA IC (IC15) is

applied to the ATM-SAR controller (IC16) and converts the

signal format into the ATM-SAR interface signal format.

The converted interface signal is applied to the ASSIST I/F

FPGA IC (IC19) to convert the signal format into the I/O sig-

nal format . The converted I/O signal is applied to the LVDS

driver (IC22) and converts the I/O signal format into the dif-

ferential signal format.

The differential signal is applied to the connected ASSIST

repeater (ID-RP2L) via [ASSIST-1 A/B] (J13) or [ASSIST-2

A/B] (J12) connector.

3-2-3 DURING LOCAL REPEATER OPERATION

(MAIN UNIT)

The data signal from the PCI/DMA FPGA IC (IC15) is

applied to the LOCAL RPT I/F FPGA IC (IC24) and converts

the signal format into the parallel data signal format.

The converted parallel data signal is applied to the buf-

fer amplifiers (IC17, IC20, IC21, IC23) and then applied to

the connected LOCAL repeater (ID-RP2D or ID-RP2V) via

[LOCAL RPT CONT I/O] connector (J10).

3-2-4 DURING CONNECTED SERVER OPERATION

(MAIN UNIT)

The data signal from the PCI/DMA FPGA IC (IC15) is

applied to the Ethernet controller (IC8) and converts the

data format into the Ethernet data format.

The converted Ethernet data is applied to the connected

server via [10BASE-T] connector (J1).