Rev. 1.40

9�

De�e��e� 1�� �01�

Rev. 1.40

93

De�e��e� 1�� �01�

BS67F340/BS67F350/BS67F360/BS67F370

Enhanced Touch A/D Flash MCU with LCD Driver

BS67F340/BS67F350/BS67F360/BS67F370

Enhanced Touch A/D Flash MCU with LCD Driver

Watchdog Timer

The Watchdog Timer is provided to prevent program malfunctions or sequences from jumping to

unknown locations, due to certain uncontrollable external events such as electrical noise.

Watchdog Timer Clock Source

The Watchdog Timer clock source is provided by the internal RC oscillator, f

LIRC

. The LIRC internal

oscillator has an approximate frequency of 32 kHz and this specified internal clock period can vary

with V

DD

, temperature and process variations. The Watchdog Timer source clock is then subdivided

by a ratio of 2

8

to 2

18

to give longer timeouts, the actual value being chosen using the WS2~WS0

bits in the WDTC register.

Watchdog Timer Control Register

A single register, WDTC, controls the required timeout period as well as the enable/disable

operation. This register controls the overall operation of the Watchdog Timer.

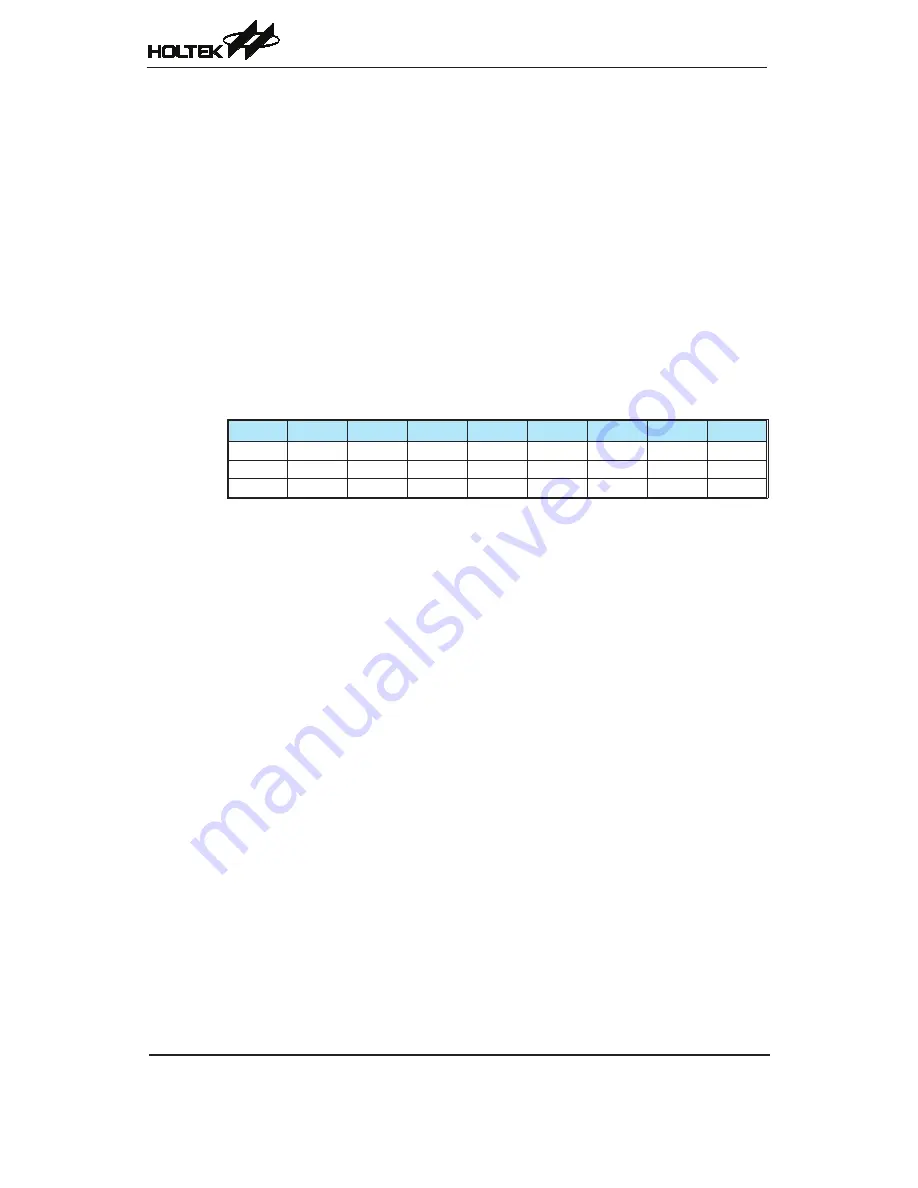

WDTC Register

Bit

7

6

5

4

3

2

1

0

Name

WE4

WE3

WE�

WE1

WE0

WS�

WS1

WS0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

POR

0

1

0

1

0

0

1

1

Bit 7~3

WE4~WE0

: WDT function enable control

10101 or 01010: Enabled

Other values: Reset MCU

If these bits are changed due to adverse environmental conditions, the microcontroller

will be reset. The reset operation will be activated after 2~3 LIRC clock cycles and the

WRF bit in the RSTFC register will be set to 1.

Bit 2~0

WS2~WS0

: WDT time-out period selection

000: 2

8

/f

LIRC

001: 2

10

/f

LIRC

010: 2

12

/f

LIRC

011: 2

14

/f

LIRC

100: 2

15

/f

LIRC

101: 2

16

/f

LIRC

110: 2

17

/f

LIRC

111: 2

18

/f

LIRC

These three bits determine the division ratio of the watchdog timer source clock,

which in turn determines the time-out period.