Chapter 10 Troubleshooting

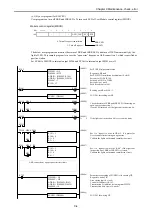

(5) Send error

ERR LED light and

STS LED blink two times

There is a possibility that the sending and receiving

processing has not endedwithin the cycle time.

Confirm whether the sending and receiving time is in

the set time of the cycle.

Calculate the sending and receiving time referring to

"Appendix A.2 Response performance of ASR

communication".

There is a possibility of

transmitting the next data before

turning on the transmission

complete flag.

Confirm the set timing of the

event sending request bit.

N

Y

Cyclic send

Supplement

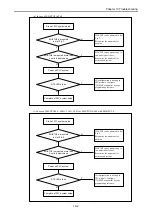

[When you do ASR cyclic communication by the combination with EHV-CPU]

When EHV-CPU is done from stop to run, it may become a send error. Because of the relations of the number

of ASR I/O area data and cyclic time. It is that because the "run beginning process" of CPU is superior to ASR

communication. Therefore transmission process did not end in cyclic time.After it shifts in the state of running,

it communicates normally. In this case, clear the error with ladder program. (Refer to following sample program

11)

*1: For instance, the cyclic time is one second, and transmission time is 0.8 - 0.9 second.

Refer to "Appendix A.2 Response performance of ASR communication" for calculating the response time.

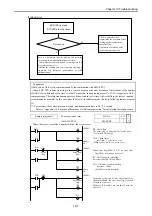

Sample program 11

To execute error reset

Slot No.

0 1 2

(For EHV-CPU)

EH-ETH2 -

-

*

When the error occurs after it begins to drive, the error is reset.

R0

(00001)

R0 : Check flag

The error flag is observed for "cyclic time +

1sec" after RUN begins.

TD0 : Check timer

Set Time

:

Cyclic time + 1sec

(When cyclic time is 1sec, set to 2sec)

R7E

(00002)

Y21

(00003)

R0

R0

TD0

R1

X20

R1

TD1

TD0

Y21

TD1

DIF

R0

R1

S

R

100ms

20

10ms

10

When error flag(X200) is ON, set error clear

flag(Y216) is turned on by set coil.

R1 : ON flag of error clear flag

Set error clear flag ON for 100ms.

TD1 : ON timer of error clear flag

Set time

:

100ms

(For 50ms or more necessity)

In the end at the time of error clear flag ON or

the observed end, the error clear flag is turned

off with the reset coil.

Moreover, R0 and R1 are turned off with the

reset coil.

R

R

Error

flag

Error clear

flag

Error clear

flag

10-7