Service manual CL2554AN / CL2854AN

- 35 -

In the type TDA9367, intended for 90° picture tubes the following geometry parameters can be

adjusted:

·

Horizontal shift

·

Vertical amplitude

·

Vertical slope

·

S-correction

·

Vertical shift

The types which are intended to be used in combination with 110° picture tubes have an East-West

control circuit. The additional controls for these types are:

·

EW width

·

EW parabola width

·

EW upper and lower corner parabola correction

·

EW trapezium correction

·

Vertical zoom, horizontal parallelogram and bow correction.

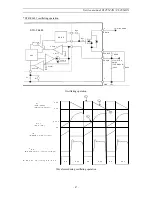

Chroma and luminance processing

The chroma band-pass and trap circuits (including the SECAM cloche filter) are realised by means of

gyrators and are tuned to the right frequency by comparing the tuning frequency with the reference

frequency of the colour decoder. The luminance delay line and the delay cells for the peaking circuit are

also realised with gyrators. The circuit contains a black stretcher function which corrects the black

level for incoming signals which have a difference between the black level and the blanking level.

Colour decoder

The ICs can decode PAL, NTSC and SECAM signals. The PAL/NTSC decoder does not need external

reference crystals but has an internal clock generator which is stabilised to the required frequency by

using the 12 MHz clock signal from the reference oscillator of the

m

-Controller/Teletext decoder.

The Automatic Colour Limiting (ACL) circuit (switchable via the ACL bit in subaddress 2OH)

prevents oversaturation occurring when signals with a high chroma-to-burst ratio are received. The

ACL circuit is designed such that it only reduces the chroma signal and not the burst signal. This has

the advantage that the colour sensitivity is not affected by this function.

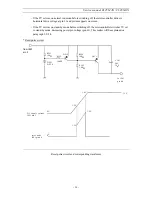

SOFTWARE CONTROL

The CPU communicates with the peripheral functions using Special function Registers (SFRS) which

are addressed as RAM locations. The registers for the Teletext decoder appear as normal SFRs in the

m

-Controller memory map and are written to these functions by using a serial bus. This bus is

controlled by dedicated hardware which uses a simple handshake system for software synchronisation.

For compatibility reasons and possible re-use of software blocks, the TV processor is controlled by I2C

bus. The TV processor control registers cannot be read. Only the status registers can be read ( Read

address 8A ).

The SECAM decoder contains an auto-calibrating PLL demodulator which has two references, via the

divided 12 MHz reference frequency (obtained from the

m

-Controller) which is used to tune the PLL to

Содержание CL2554AN

Страница 17: ...Service manual CL2554AN CL2854AN 16 ...

Страница 21: ...Service manual CL2554AN CL2854AN 20 ...

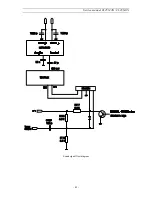

Страница 34: ...Service manual CL2554AN CL2854AN 33 5 Circuit description 5 1 Block diagram ...

Страница 39: ...Service manual CL2554AN CL2854AN 38 Chassis block diagram IF ...

Страница 43: ...Service manual CL2554AN CL2854AN 42 Sound signal flow diagram ...

Страница 56: ...Service manual CL2554AN CL2854AN 55 ...