FabIATech Corporation

57

Bit 4: Clear to Send (CTS)

Bit 5: Data Set Ready (DSR)

Bit 6: Ring Indicator (RI)

Bit 7: Received Line Signal Detect (RSLD)

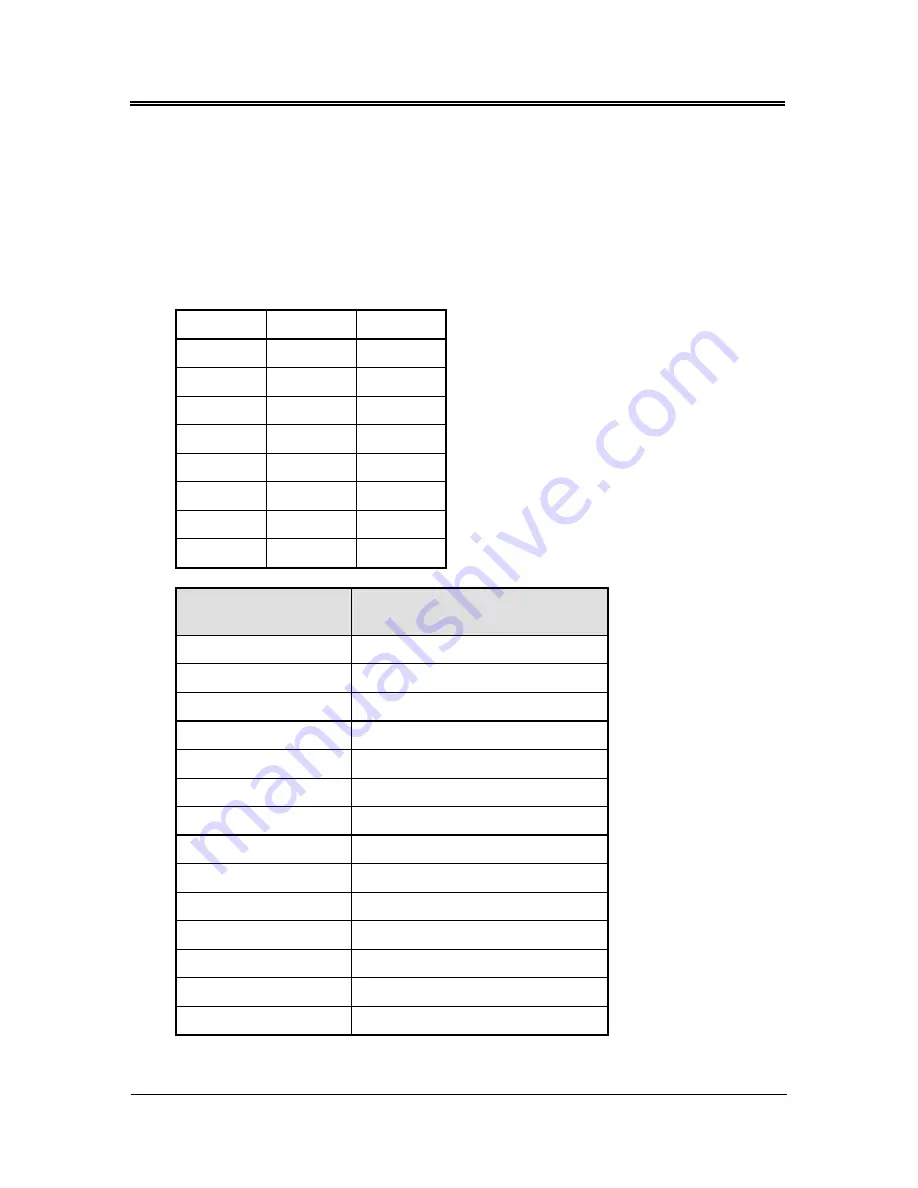

Divisor Latch (LS, MS)

LS

MS

Bit 0:

Bit 0

Bit 8

Bit 1:

Bit 1

Bit 9

Bit 2:

Bit 2

Bit 10

Bit 3:

Bit 3

Bit 11

Bit 4:

Bit 4

Bit 12

Bit 5:

Bit 5

Bit 13

Bit 6:

Bit 6

Bit 14

Bit 7:

Bit 7

Bit 15

Desired Baud

Rate

Divisor Used to Generate 16x

Clock

300 384

600 192

1200 96

1800 64

2400 48

3600 32

4800 24

9600 12

14400 8

19200 6

28800 4

38400 3

57600 2

115200 1

Содержание FX5401

Страница 5: ...v ...

Страница 8: ...FabIATech Corporation 3 Layout 18 30V 2 1 1 2 18 30V 1 1 2 2 ...

Страница 11: ...FabIATech Corporation 6 ...

Страница 19: ...FabIATech Corporation 14 ...

Страница 41: ...FabIATech Corporation 36 ...

Страница 51: ...FabIATech Corporation 46 ...

Страница 52: ...FabIATech Corporation 47 Appendix Dimension 200 44 2 130 70 26 48 70 8 17 R4 5 R2 3 6 ...