CHAPTER 26:PCMPWM

988

S6J3200 Series Hardware Manual Document Number: 002-04852 Rev. *G

3.2.

PWM Cycle Time Configuration

The free running counter used in the PCM to PWM conversion process determines the cycle time of the

generated PWM signal. The PWM cycle time is equal to the counter's full count period. So, the cycle time

computes as follows:

T

PWM

=

𝐶𝑂𝑈𝑁𝑇𝑃 + 1

f

counter

The countp parameter is configured in the PCMPWMi_COUNTP register. The count frequency of the

counter may be configured in the PCMPWMi_CLKSEL register. It determines the counter clock by

dividing the PWM clock PWM_CLK by 1, 2, 4 or 8. So, the final formula for the PWM cycle time results to:

T

PWM

=

(𝐶𝑂𝑈𝑁𝑇𝑃 + 1) × 2

CLKSEL

f

PWM_CLK

3.3.

PCM Data Sample Input

The PCM to PWM conversion block reads the PCM data samples from a FIFO buffer. To ensure

continuous operation of the PCM to PWM conversion, it is essential to provide the FIFO buffer with the

same sustained rate of PCM data samples. The required frequency for the data samples corresponds to

the reciprocal of the PWM cycle time:

f

sample

=

f

PWM_CLK

(𝐶𝑂𝑈𝑁𝑇𝑃 + 1) × 2

CLKSEL

The data samples may be provided by the CPU or may be transferred via DMA. For a CPU based

transfer there is support for requesting data by interrupt. Alternatively the CPU may poll the interrupt

status register to determine, if there is free space in the FIFO buffer. Regardless of how the buffer FIFO is

supplied with data samples, the PCMPWMi_CONTROL:FEST field specifies, at which number of free

FIFO buffer entries the data transfer is requested. If the number of free entries exceeds that specified in

the FEST field, the PCMPWMi_INTRSTAT:DREQ status bit is set and an interrupt request may be

asserted or another DMA data transfer may be initiated.

If the PCM to PWM conversion tries to read a PCM data sample from the FIFO buffer and finds it empty, it

uses the PCM value instead. I.e. the module outputs the last PWM pattern again, if no PCM data is

supplied. To detect this error case of FIFO buffer under-run, an interrupt request is asserted.

Please note the above formula limits the resolution of the PCM to PWM conversion at a given f

PWM_CLK

and f

sample

. E.g. at a clock frequency of 80 MHz, a sample frequency of 19.5 kHz, and CLKSEL set to zero,

the counter may count to 4103 only. This corresponds to a resolution of about 12 bits. Table 3-3 shows

some examples for the configuration of the PCMPWM module and the resulting sample frequencies and

resolutions.

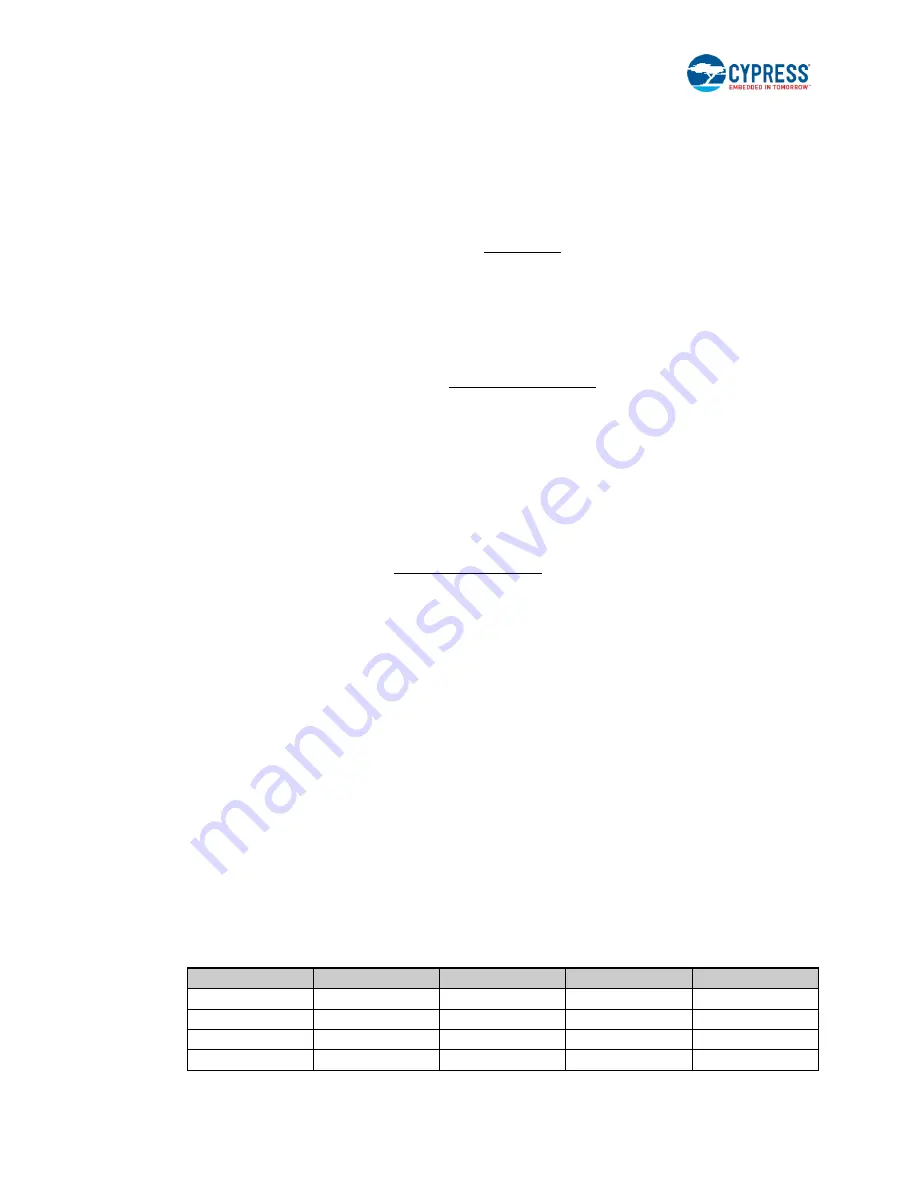

Table 3-3 Configuration Examples

f

PWM_CLK

CLKSEL

COUNTP

f

sample

Resolution

80 MHz

0

4,095

19.53 kHz

12 bit

80 MHz

0

65,535

1.22 kHz

16 bit

80 MHz

2

255

78.13 kHz

8 bit

100 MHz

1

1,023

48.83 kHz

10 bit

Содержание S6J3200 Series

Страница 1041: ...CHAPTER 28 LCD Controller 1040 S6J3200 Series Hardware Manual Document Number 002 04852 Rev G...

Страница 1044: ...CHAPTER 28 LCD Controller S6J3200 Series Hardware Manual Document Number 002 04852 Rev G 1043...

Страница 1047: ...CHAPTER 28 LCD Controller 1046 S6J3200 Series Hardware Manual Document Number 002 04852 Rev G...

Страница 1050: ...CHAPTER 28 LCD Controller S6J3200 Series Hardware Manual Document Number 002 04852 Rev G 1049...

Страница 1084: ...CHAPTER 28 LCD Controller S6J3200 Series Hardware Manual Document Number 002 04852 Rev G 1083...

Страница 1086: ...CHAPTER 28 LCD Controller S6J3200 Series Hardware Manual Document Number 002 04852 Rev G 1085...

Страница 1088: ...CHAPTER 28 LCD Controller S6J3200 Series Hardware Manual Document Number 002 04852 Rev G 1087...