CHAMP-AV8 (VPX6-462) H

ARDWARE

U

SER

’

S

M

ANUAL

C

URTISS

-W

RIGHT

1-18

P

ROPRIETARY

826448 V

ERSION

5 M

ARCH

2015

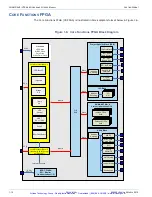

Figure 1.8: CHAMP-AV8 Serial Port Implementation

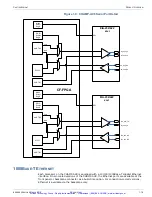

Access to the two dual-mode EIA-232/422 transceivers are multiplexed by the FPGA between

DIO[16] and UART A0 (also between DIO[17] and UART B0). This allows a DIO port to take

control of a EIA-422 differential pair, thus forming a DDIO (Differential DIO) port. Figure 1.9,

“CHAMP-AV8 Serial Port Detail,” on page 1-19 illustrates how the control registers are used to

control switching between the DIO registers, UART ports, and the EIA-232/422 dual-mode

transceiver.

Node

B

Intel®

PCH

Front Panel

Connector

Node

A

Intel®

PCH

LPC_A

A0/A1

RS-232/422

Transceiver

ISL 3333

1 RS 422 CH or

2 RS 232 CH

TX

TX

RX

RX

B0/B1

RS-232/422

Transceiver

ISL 3333

TX

TX

RX

RX

Backplane Connector

CF- FPGA

SEL

SEL

REG

UART

A1

UART

A0

UART

B1

UART

B0

REG

LPC_B

UART

A2

UART

B2

UART

A3

RS- 422

XCVR

RS- 422

XCVR

IPMI BMC

1 RS 422 CH or

2 RS 232 CH

TX

p/ n

RX

p/n

TX

p/n

RX

p/n

1 RS 422 CH

A0

A1

B0

B1

LTC2855

LTC2855

1 RS 422 CH

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com