C

URTISS

-W

RIGHT

1

826448 V

ERSION

5 M

ARCH

2015

P

ROPRIETARY

A-15

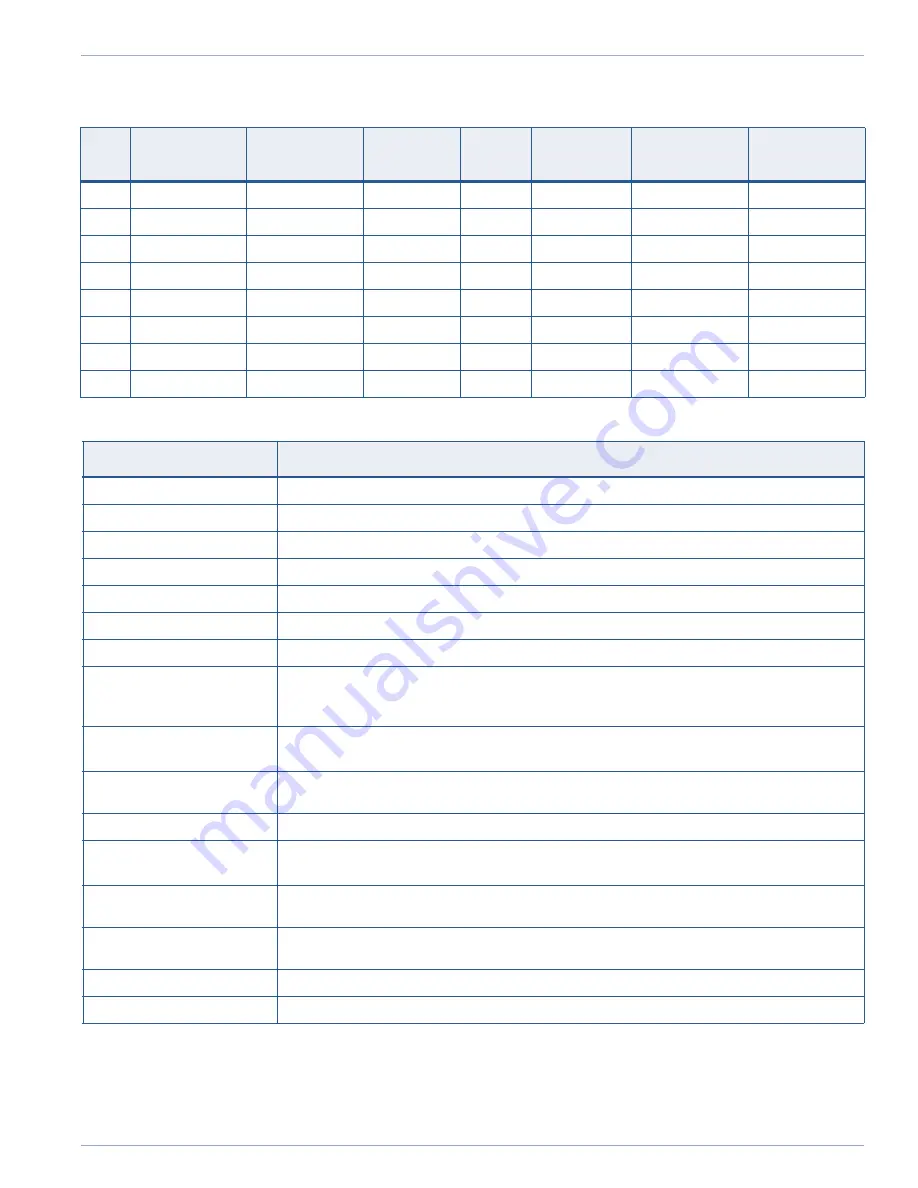

Table A.3:

P0 Utility Connector Pin Assignments

Wafer

No.

Row G

Signal

Row F

Signal

Row E

Signal

Row D

Signal

Row C

Signal

Row B

Signal

Row A

Signal

1

Vs1_BP12V

Vs1_BP12V

Vs1_BP12V

NC

Vs2_BP12V

Vs2_BP12V

Vs2_BP12V

2

Vs1_BP12V

Vs1_BP12V

Vs1_BP12V

NC

Vs2_BP12V

Vs2_BP12V

Vs2_BP12V

3

Vs3_NC_BP_5V

Vs3_NC_BP_5V

Vs3_NC_BP_5V NC

Vs3_NC_BP_5V Vs3_NC_BP_5V

Vs3_NC_BP_5V

4

SM2_BP_I2C1_SCL SM3_BP_I2C1_DAT GND

-12V_AUX

GND

SYSRST_L

NVMRO

5

GAP_L

GA4_L

GND

3.3V_AUX

GND

SM0_BP_I2C0_SCL SM1_BP_I2C0_DAT

6

GA3_L

GA2_L

GND

+12V_AUX GND

GA1_L

GA0_L

7

TCK

GND

TDO

TDI

GND

TMS

TRST_L

8

GND

REF_CLK_N

REF_CLK_P

GND

BP_AUX_CLK_N BP_AUX_CLK_P

GND

Table A.4:

P0 Utility Connector Signal Definitions

CHAMP-AV8 Signal

Description

Vs1_BP12V

+12V Power; 12V ± 5%, Max Nominal Ripple

≤

240 mV, up to 24 A - Vs1

Vs2_BP12V

+12V Power; 12V ± 5%, Max Nominal Ripple

≤

240 mV, up to 24 A - Vs2

Vs3_NC_BP_5V

No Connect - Vs3

3.3V_AUX

+3.3V Auxiliary Power; 3.3V±5%, Nominal Ripple

≤

30 mV; 1 A max

+12V_AUX

+12V Power; 12V ± 5%, Nominal Ripple

≤

50 mV; 1 A max

-12V_AUX

-12V Power; -12V ± 5%, Nominal Ripple

≤

50 mV; 1 A max

GA4_L:GA0_L; GAP_L

Geographical Address Inputs 0-4 and Parity; Must pull-up to 3.3V on-board.

NVMRO

Non-Volatile Memory Read Only - Active high signal that prevents any non-volatile memory from being

updated; pulled-up to 3.3VAUX on backplane; can only be driven low by backplane.

Note

: this signal does not write-enable the PABS (Permanent Alternate Boot Select) Flash memory.

REF_CLK_P

REF_CLK_N

Differential bussed reference clock; 25 MHz ±100 ppm; 45% to 55% duty cycle; M-LVDS signaling; rise and

fall time > 1 ns; driven by SYS_CON.

SYSRST_L

System Reset; pulled-up to 3.3VAUX on backplane; usually driven by SYSCON but can be driven by any

board in the system.

TCLK, TDO, TDI, TMS, TRST_L

JTAG Signals; TCLK, TDO, and TDI are pulled-up to 3.3V on-board; TRST_L is pulled-down.

BP_AUX_CLK_P

BP_AUX_CLK_N

Differential bussed reference clock; 1 Hz +50 ppm; minimum pulse width of 100 µs; LVDS signaling; rise and

fall time

≥

1 ns; driven by SYS_CON.

SM0_BP_I2C0_SCL,

SM1_BP_I2C0_DAT

System management I

2

C bus number 1.

SM2_BP_I2C1_SCL,

SM3_BP_I2C1_DAT

System management I

2

C bus number 2.

NC

No connect.

GND

Ground signals as defined in VITA 46.0.

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com