CDB43198-GBK

52

DS1156DB1

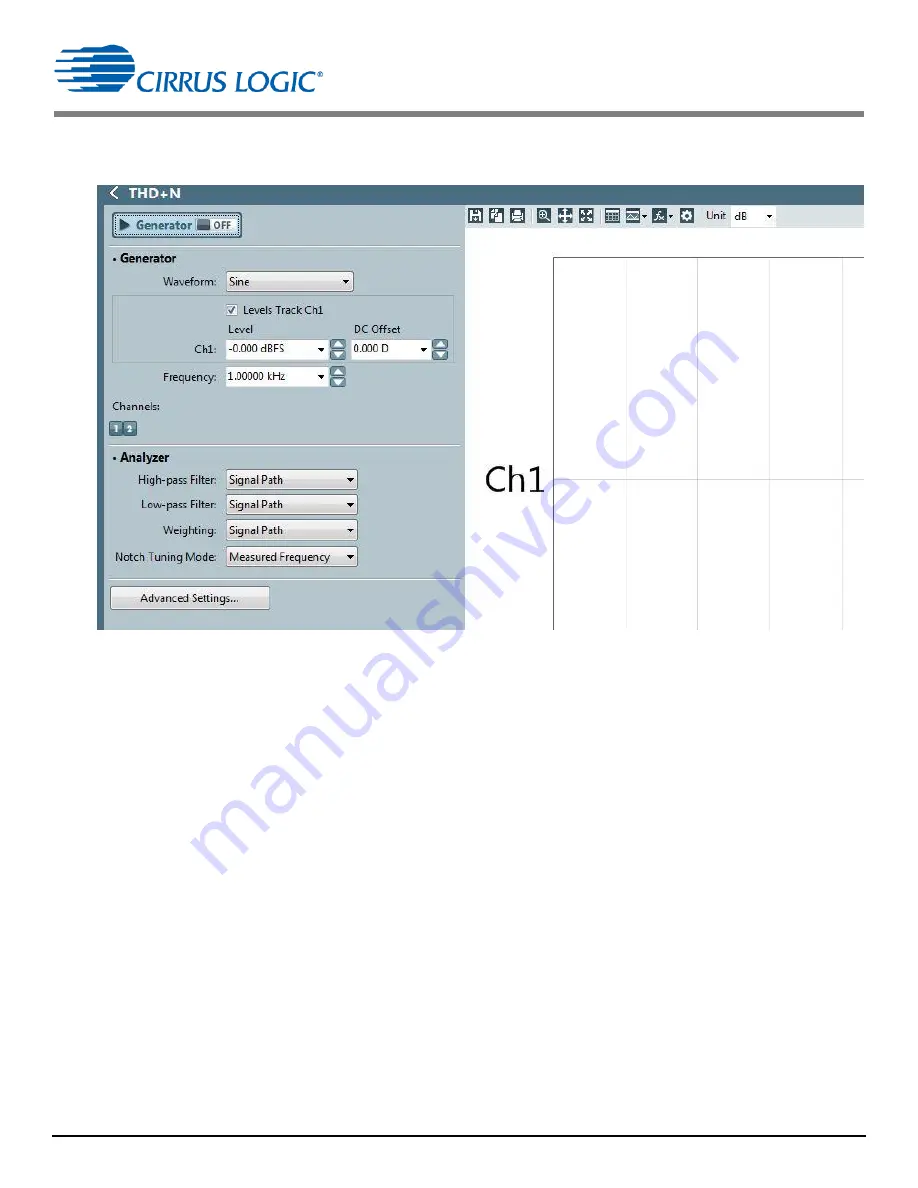

8. To run THD+N test, configure the Input Level and Bandwidth as shown below. Click on the "Generator" button to

run the test. THD+N ratio will be displayed for both channels. THD+N ratio is typically displayed in Percentage (%).

To display the values in dB, select "dB" from the drop down menu next to Unit on top of the display.

Figure 48 THD+N Measurement Settings