3

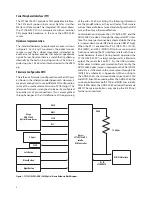

Figure 2. CY7C63743-PXC –ADNS-3080 Optical Mouse Hardware Block Diagram.

Serial Peripheral Interface (SPI)

The CY7C63743-PXC provides a SPI compatible interface.

The SPI circuit supports byte serial transfer in either

Master or Slave mode. The integrated SPI circuit allows

the CY7C63743-PXC to communicate with an external

SPI compatible hardware, in this case the ADNS-3080

sensor.

Hardware Implementation

The standard hardware to implement a mouse is shown

in Figure 2. For X and Y movement, the optical mouse

sensor is used. The Z wheel movement is detected by

another set of optical encoder that outputs quadrature

signals. For each button there is a switch that is pulled up

internally by the built-in in pull up resistors. The D-line is

pulled up via a 1.3k ohm resistor connected to the VREG

pin.

Firmware Confi gurable GPIO

The reference fi rmware is confi gured to use the GPIO pins

as shown in the schematic under Appendix A. However, it

may be more optimal to use a diff erent I/O confi guration

to meet the mechanical constraints of PCB design. The

reference fi rmware is designed to be easily confi gured

to another set of pin connections. This is accomplished

through changes in the I/O defi nitions at the beginning

of the adns- 3080.asm listing. The following statements

are the pin defi nitions as they exist today. The fi rmware

will use these defi nitions to read and confi gure the GPIO

pins, without any other modifi cations.

Communications between the CY7C63743-PXC and the

ADNS-3080 are done through the integrated SPI inter-

face. The serial port cannot be activated while the chip

is in power down mode (NPD low) or reset (RESET high).

When the SPI is enabled thru P0.4 (NCS), P0.7 (SCLK),

P0.6 (MISO), and P0.5 (MOSI) GPIO pins serve as special

functions enabling the SPI interface to talk with the ex-

ternal hardware. (Sensor) During normal operation, the

CY7C63743-PXC SPI is always confi gured as a Master to

output the serial clock on P0.7. So, the USB microcon-

troller always initiates communication. Data sent by the

ADNS-3080 optical sensor is received on the P0.6 (MISO),

and data is shifted out to the same sensor through P0.5

(MOSI). See schematic in Appendix A. When writing to

the ADNS-3080, the microcontroller drives both SCLK

and MOSI lines. When reading from the ADNS-3080, the

microcontroller drives both SCLK and MOSI lines initially.

After tSRAD delay, the ADNS-3080 will drive the data via

MISO. The microcontroller is only driving the SCLK line (

for the serial interface).

Avago

ADNS-3080

Optical Mouse Sensor

Wheel Button

Right Button

Z Optics

Cypress

CY7C63743A-PC

enCoRe

USB Controller

USB/PS2 Interface

MISO

MOSI

SCLK

NCS

D+/D-

SCLK/SDATA

VREG

1.3 k Ohm

Left Button

Z LED