12

CheckWheel

– This function checks whether the proper

sequence of commands have been issued by the host

to enable the wheel of the mouse. The sequence is three

consecutive setting rate commands of 200, 100 and 80

reports per second.

send_1

– sends a PS/2 1 bit

send_0

– sends a PS/2 0 bit

GetBit

– receives a PS/2 bit from the host

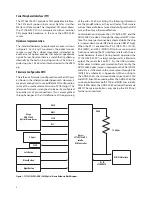

Interrupt Service Routines (ISR)

The CY7C63743-PXC features 12 different sources of

interrupts. There are only four ISRs implemented in this

application. If an interrupt is enabled and the conditions

for the interrupts are met, the microcontroller will gener-

ate an interrupt. Upon servicing the interrupt, the hard-

ware will fi rst disable all interrupts by clearing the Global

Interrupt Enable bit. This is followed by an automatic

CALL instruction to the ROM address of the interrupt

being serviced in the Interrupt Vector. The instruction in

the Interrupt Vector is typically a JMP instruction to the

Interrupt Service Routine (ISR). A RETI or RET instruction

at the end of the ISR brings the program counter (PC)

back to the location prior to the interrupt (POR and USB

Bus Reset are exceptions).

DualMain

– When power is fi rst applied to the CY7C63743-

PXC, a Power On Reset (POR) occurs; the microcontroller

starts executing code from address 0x00. This is a JMP

instruction to the

DualMain

routine. This routine initial-

izes the program stack pointer (PSP), data stack pointer

(DSP), ram variables, and the GPIO pins. This routine calls

GetMouseType

which returns the interface of the mouse.

If a USB interface is detected, the program jumps to

the

usbMain

loop. Otherwise, the program goes to the

ps2Main

loop.

DualUsbBusReset_ps2Error

– The USB-PS2 Interrupt Mode bit

in the USB Status and Control Register is defaulted to

“0”, or USB mode. This indicates that the USB Bus Reset

interrupt will be generated if the SE0 condition (D+ and

D- are both LOW) exists for 256us. This ISR enables the

USB Device Address, sets up the endpoint modes and

jumps to

usbMain

for the USB initialization.

Dual1msTimer

– This ISR reads the current status of the

buttons. Therefore, every one millisecond the button

state is updated; the button status information will be

used by the

ProcessButtons

function at a later time. This

ISR maintains the

dualInterface1ms

counter variable

which is used as a 1ms timing reference in other parts

of the program. This routine also handles the entrance

or exit from suspend. The mouse will prepare to enter

a suspend (low power) state if there is no bus activity in

3ms. If the mouse is confi gured for remote wakeup, the

Bus Reset and wakeup interrupts are enabled prior to sus-

pending the chip. The program then enters a suspended

state, and will wake at least as often as the wakeup timer

interrupts or as a result of the USB Bus Reset interrupt.

Each time the chip wakes up due to the wake up timer

interrupt, the state of the buttons is examined by the

GetButtons

function. If a change in the button state has

occurred, the mouse will generate a resume signal to

the host and exit the ISR. If the device is not enabled

for remote wakeup, only the USB bus reset interrupt is

enabled, and the part is suspended. Only a Bus Reset can

wake up the chip. If the resume was due to bus activity,

the fi rmware returns to the main loop. If the resume was

due to a button press, a K state is driven upstream for 14

milliseconds prior to returning to the main loop. Moving

the mouse will not wake the suspended system.

DualUsbEndpoint0_ps2Error

– This ISR is entered upon receiv-

ing an Endpoint 0 interrupt. Endpoint 0 interrupts occur

during the Setup, data, and status phases of a control

transfer. This ISR handler jumps to the proper routine to

handle one of these phases.

DualUsbEndpoint1_ps2Error

– This ISR is entered upon re-

ceiving an Endpoint 1 interrupt. If the ACK bit is set,

indicating that a mouse packet was just transmitted

to the host successfully, the SIE automatically sets the

endpoint mode to NAK_IN mode, and the data toggle

bit is fl ipped for the next transaction. The data toggle bit

should never be toggled if the interrupt was a result of a

NAK transaction.