63

AT94KAL Series FPSLIC

Rev. 1138G–FPSLI–11/03

The MCU after five CPU clock-cycles, and can be used when an external clock signal is

applied to the XTAL1 pin. This setting does not use the WDT oscillator, and enables very fast

start-up from the Sleep, Power-down or Power-save modes if the clock signal is present dur-

ing sleep.

RESET can be connected to V

CC

directly or via an external pull-up resistor. By holding the pin

Low for a period after V

CC

has been applied, the Power-on Reset period can be extended.

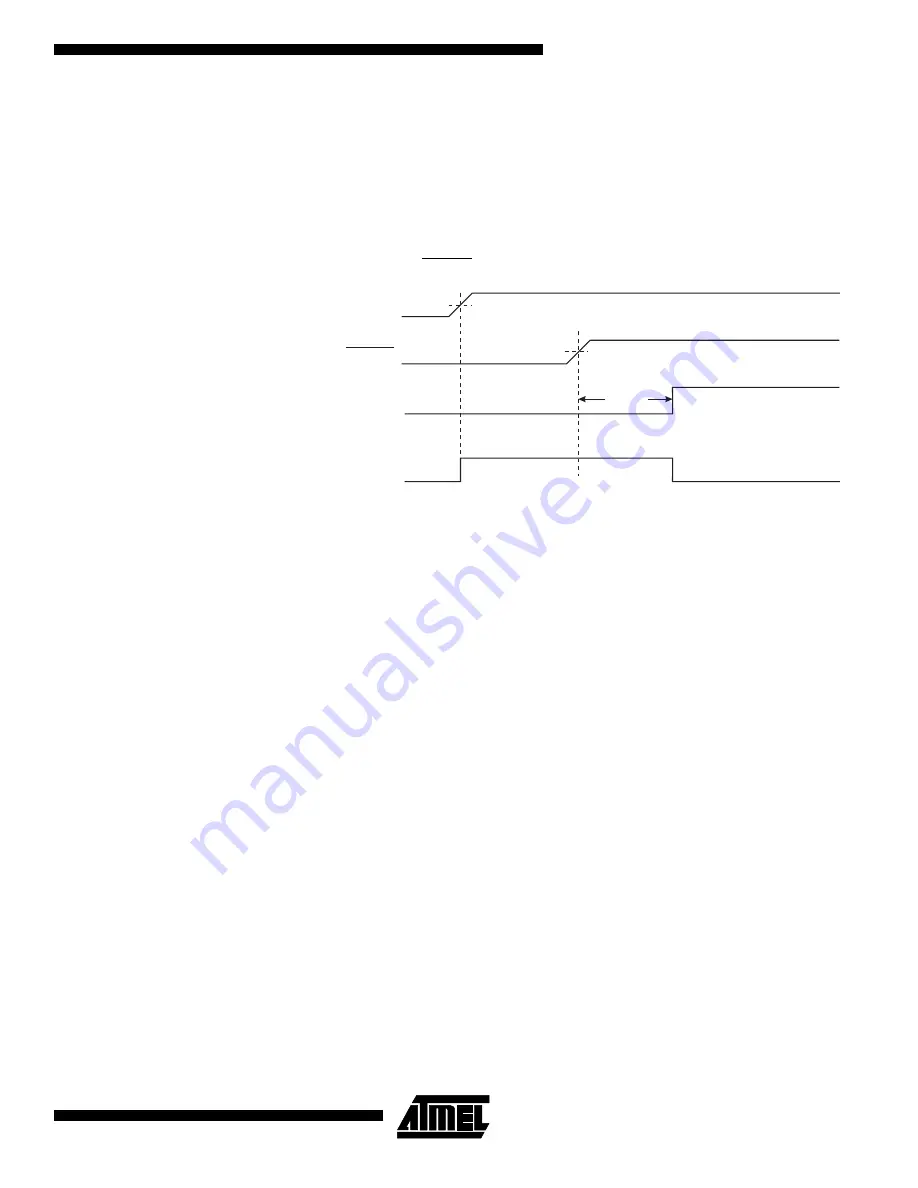

Refer to Figure 38 for a timing example on this.

Figure 38.

MCU Start-up, RESET Controlled Externally

External Reset

An external reset is generated by a low-level on the AVRRESET pin. When the applied signal

reaches the Reset Threshold Voltage – V

RST

– on its positive edge, the delay timer starts the

MCU after the Time-out period t

TOUT

has expired.

Watchdog Reset

When the Watchdog times out, it will generate a short reset pulse of 1 XTAL cycle duration.

On the falling edge of this pulse, the delay timer starts counting the Time-out period t

TOUT

.

Time-out period t

TOUT

is approximately 3 µs – at V

CC

= 3.3V. the period of the time out is volt-

age dependent.

Software Reset

See “Software Control of System Configuration” on page 51.

Interrupt Handling

The embedded AVR core has one dedicated 8-bit Interrupt Mask control register: TIMSK –

Timer/Counter Interrupt Mask Register. In addition, other enable and mask bits can be found

in the peripheral control registers.

When an interrupt occurs, the Global Interrupt Enable I-bit is cleared (zero) and all interrupts

are disabled. The user software can set (one) the I-bit to enable nested interrupts. The I-bit is

set (one) when a Return from Interrupt instruction (RETI) is executed.

When the Program Counter is vectored to the actual interrupt vector in order to execute the

interrupt handling routine, the hardware clears the corresponding flag that generated the inter-

rupt. Some of the interrupt flags can also be cleared by writing a logic 1 to the flag bit

position(s) to be cleared.

If an interrupt condition occurs when the corresponding interrupt enable bit is cleared (zero),

the interrupt flag will be set and remembered until the interrupt is enabled, or the flag is

cleared by software.

If one or more interrupt conditions occur when the global interrupt enable bit is cleared (zero),

the corresponding interrupt flag(s) will be set and remembered until the global interrupt enable

bit is set (one), and will be executed by order of priority.

The status register is not automatically stored when entering an interrupt routine and restored

when returning from an interrupt routine. This must be handled by software.

RESET

TIME-OUT

INTERNAL RESET

t

TOUT

V

RST

V

CC

V

POT