329

8331B–AVR–03/12

Atmel AVR XMEGA AU

26.3

Operation

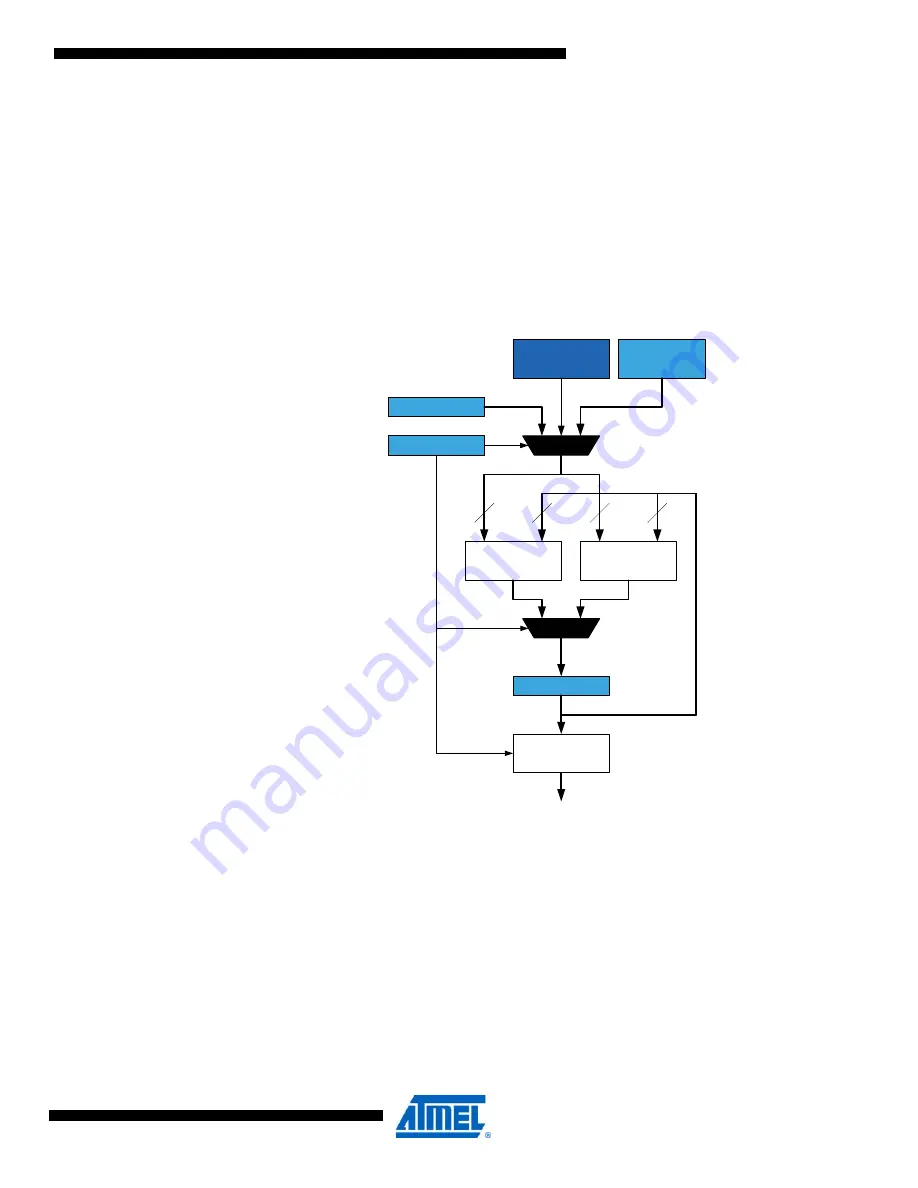

The data source for the CRC module must be selected in software as either flash memory, the

DMA channels, or the I/O interface. The CRC module then takes data input from the selected

source and generates a checksum based on these data. The checksum is available in the

CHECKSUM registers in the CRC module. When CRC-32 polynomial is used, the final check-

sum read is bit reversed and complemented (see

).

For the I/O interface or DMA controller, which CRC polynomial is used is software selectable,

but the default setting is CRC-16. CRC-32 is automatically used if Flash Memory is selected as

the source. The CRC module operates on bytes only.

Figure 26-1.

CRC generator block diagram.

26.4

CRC on Flash memory

A CRC-32 calculation can be performed on the entire flash memory, on only the application sec-

tion, on only the boot section, or on a software selectable range of the flash memory. Other than

selecting the flash as the source, all further control and setup are done from the NVM controller.

This means that the NVM controller configures the memory range to perform the CRC on, and

the CRC is started using NVM commands. Once completed, the result is available in the check-

sum registers in the CRC module. For further details on setting up and performing CRC on flash

memory, refer to

”Memory Programming” on page 431

.

DATAIN

CTRL

Flash

Memory

DMA

Controller

CRC-16

CRC-32

CHECKSUM

bit-r

complement

16

8

8

32

Checksum read

crc32