AT90S/LS4434 and AT90S/LS8535

79

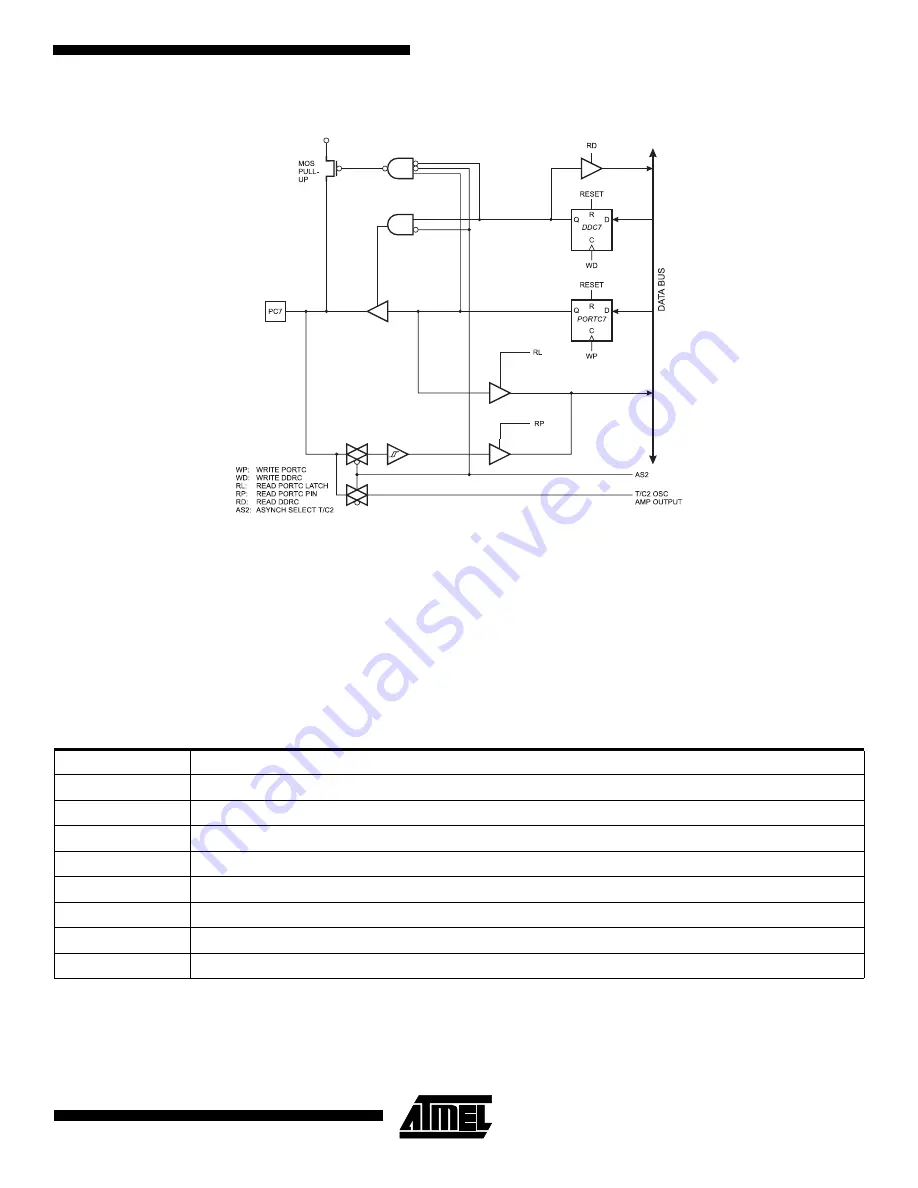

Figure 60.

Port C Schematic Diagram (Pins PC7)

Port D

Port D is an 8-bit bi-directional I/O port with internal pull-up resistors.

Three I/O memory address locations are allocated for Port D, one each for the Data Register – PORTD, $12($32), Data

Direction Register – DDRD, $11($31) and the Port D Input Pins – PIND, $10($30). The Port D Input Pins address is read-

only, while the Data Register and the Data Direction Register are read/write.

The Port D output buffers can sink 20 mA. As inputs, Port D pins that are externally pulled low will source current if the

pull-up resistors are activated.

Some Port D pins have alternate functions as shown in Table 34.

Table 34.

Port D Pin Alternate Functions

Port Pin

Alternate Function

PD0

RXD (UART Input line)

PD1

TXD (UART Output line)

PD2

INT0 (External interrupt 0 input)

PD3

INT1 (External interrupt 1 input)

PD4

OC1B (Timer/Counter1 output compareB match output)

PD5

OC1A (Timer/Counter1 output compareA match output)

PD6

ICP (Timer/Counter1 input capture pin)

PD7

OC2 (Timer/Counter2 output compare match output)