CYC1000 User Guide

www.arrow.com

Page | 18

January 2020

3.3.9.2

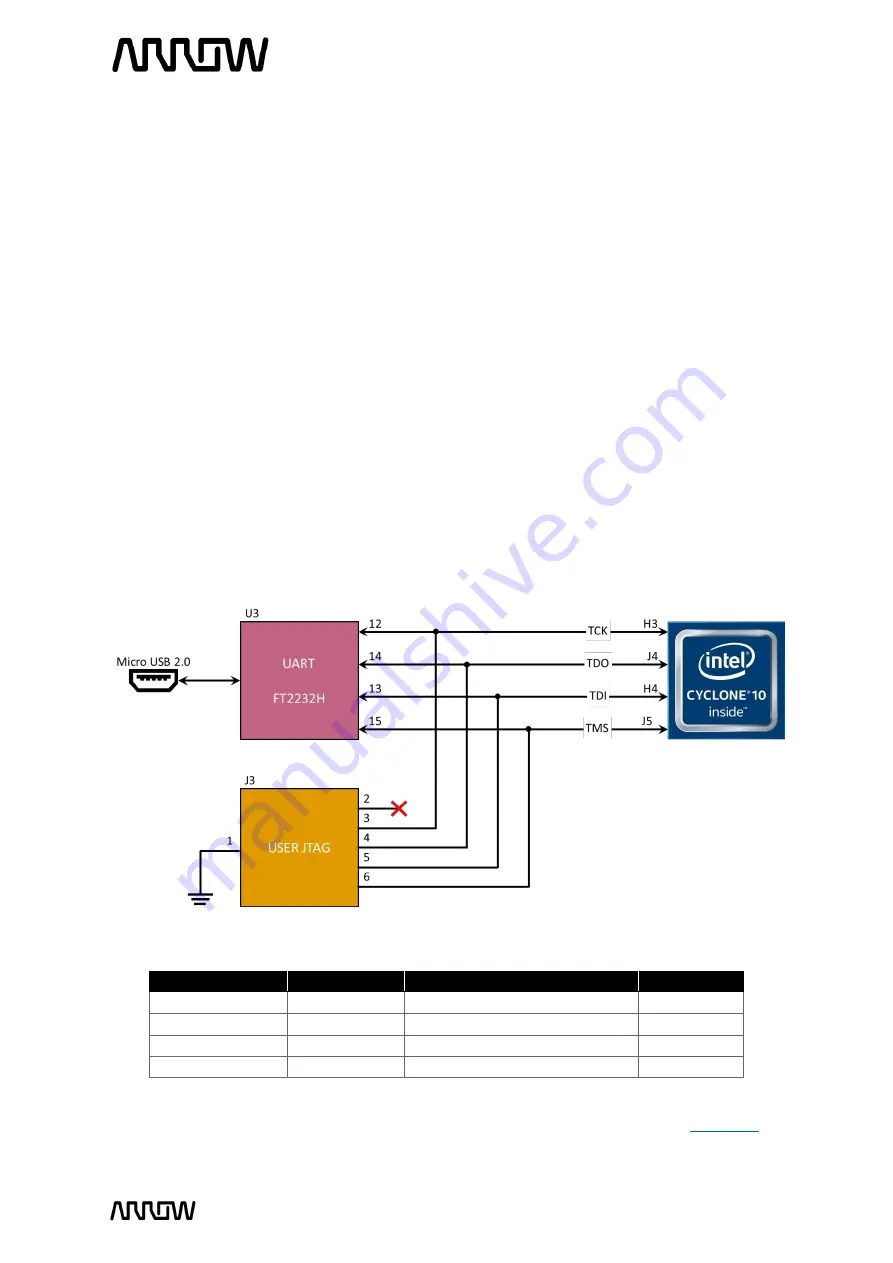

JTAG Chain Configuration

There are two types of configuration methods supported by CYC1000:

1.

JTAG Configuration:

configuration using JTAG ports. JTAG configuration scheme allows you to

directly configure the device core through JTAG pins (TDI, TDO, TMS and TCK pins). The

Quartus Prime software automatically generates a .sof that can be downloaded to the Cyclone

10 LP with a download cable through the Quartus Prime Programmer.

2.

Configuration from EPCQ-A flash:

configuration using external flash. Before configuration,

you need to program the configuration data .jic into the configuration flash memory (EPCQ-

A) which provides non-volatile storage for the bit stream. The information is retained within

EPCQ-A even if the CYC1000 is turned off. When the board is powered on, the configuration

data in the EPCQ-A is automatically loaded into the Cyclone 10 LP FPGA.

The FPGA device can be configured through JTAG interface on CYC1000, but the JTAG chain must

form a closed loop, which allows Quartus Prime programmer to detect the FPGA device.

CYC1000 offers two ways of configuring your board.

1)

Through the on-board Arrow USB Programmer2

2)

Pins for connec

ting user’s preferred JTAG interface

Board Reference

FPGA Pin No.

Description

I/O Standard

TCK

PIN_H3

Test Interface Clock

3.3 V

TDO

PIN_J4

Test Data Out

3.3 V

TDI

PIN_H4

Test Data In

3.3 V

TMS

PIN_J5

Test Mode Select

3.3 V

For detailed information about how to configure the Cyclone 10 LP, please refer to

Figure 14

–

JTAG Connections