Introduction

1-2

Copyright © 2000 ARM Limited. All rights reserved.

ARM DDI 0186A

1.1

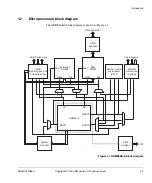

About the ARM966E-S

The ARM966E-S is a

synthesizable

macrocell combining an ARM processor with

tightly-coupled SRAM memory. It is a member of the ARM9 Thumb family of

high-performance, 32-bit

System-on-Chip

(SoC) processor solutions and is targeted at

a wide range of embedded applications where high performance, low system cost, small

die size, and low power are all important.

The ARM966E-S processor macrocell provides a complete high-performance

processor subsystem, including an ARM9E-S RISC integer CPU, tightly-coupled

SRAM for each of the instruction and data CPU interfaces, write buffer and an AMBA

AHB bus interface. Providing this complete high-frequency subsystem frees the SoC

designer to concentrate on design issues unique to their system. The synthesizable

nature of the device eases integration into ASIC technologies.

The tightly-coupled SRAMs within the ARM966E-S macrocell allow high-speed

operation without incurring the performance and power penalties of accessing the

system bus, while having a lower area overhead than a cached memory system. The size

of both the instruction and data SRAM are implementor-configurable to allow tailoring

of the hardware to the embedded application. Additionally, You can configure the data

SRAM interface to allow

Direct Memory Access

(DMA) to this RAM.

The ARM9E-S core within the ARM966E-S macrocell executes both the 32-bit ARM

and 16-bit Thumb instruction sets, allowing trade off between high performance and

high code density. Additionally the ARM9E-S features:

•

ARMv5T 32-bit instruction set with improved ARM/Thumb code interworking

and enhanced multiplier designed for improved DSP performance

•

ARM debug architecture with additional support for real-time debug, which

allows critical exception handlers to execute while debugging the system.

The ARM966E-S includes support for external coprocessors allowing floating point or

other application-specific hardware acceleration to be added.

To minimize die size and power consumption the ARM966E-S does not provide virtual

to physical address mapping as this is not required by most embedded systems. A

simple fixed memory map is implemented for the close-coupled local RAM, ideally

suited to small, fast, real-time embedded control applications.

The ARM966E-S synthesizable implementation supports the use of a scan test

methodology for the standard cell logic and

Built-In-Self-Test

(BIST) for the

tightly-coupled SRAM.

Содержание ARM966E-S

Страница 6: ...Contents vi Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 20: ...Introduction 1 4 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 48: ...Tightly coupled SRAM 4 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 80: ...Bus Interface Unit 6 20 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 118: ...Debug Support 8 26 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 130: ...Test Support 10 8 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 142: ...Instruction cycle timings 11 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 158: ...Signal Descriptions A 16 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 176: ...AC Parameters B 18 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...