UG-386

AD9642/AD9634/AD6672 User Guide

Rev. A | Page 12 of 26

5.

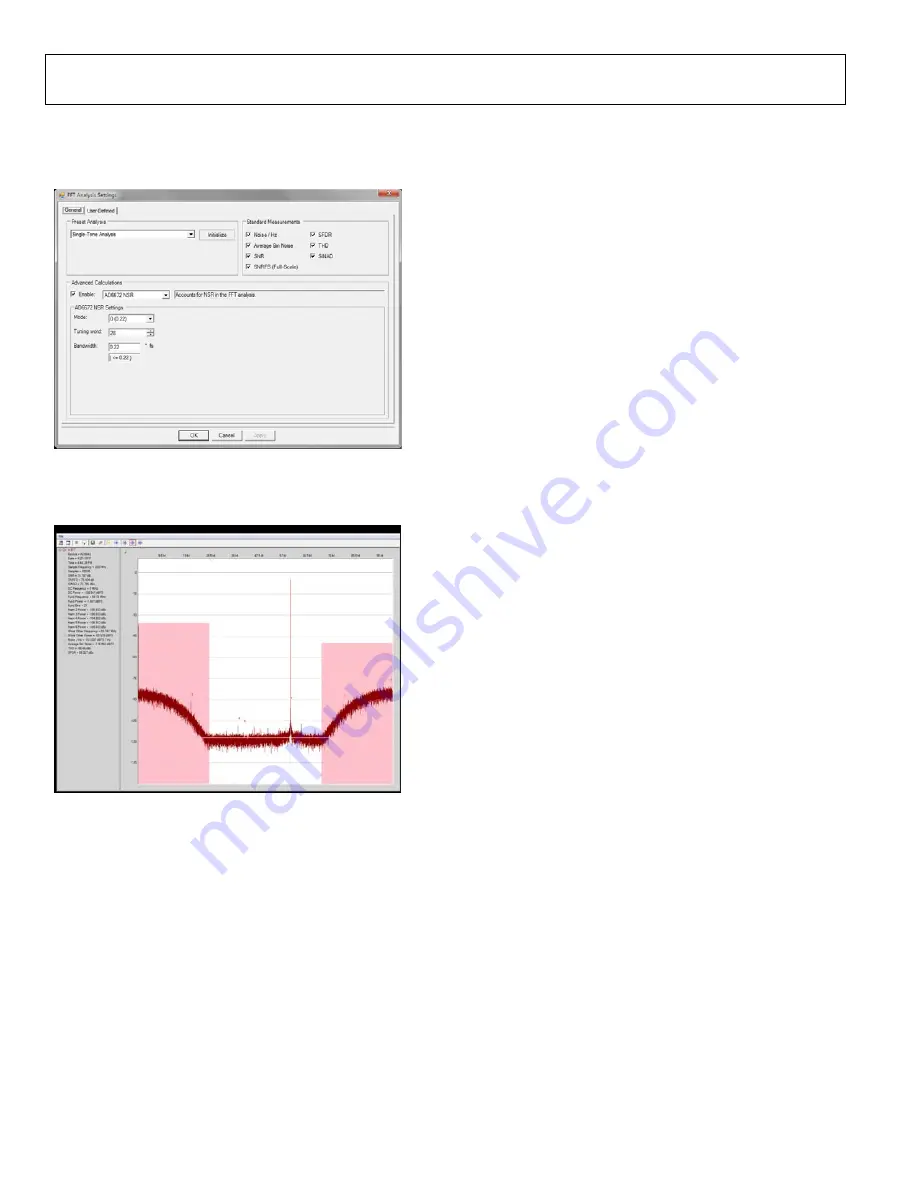

Configure the settings in the FFT analysis to match the

settings selected for the NSR in the SPI controller (see

Figure 16).

10

59

3-

01

7

Figure 16. VisualAnalog, FFT Analysis Settings for

6.

The result should show an FFT plot that looks similar to

Figure 17.

10

59

3-

01

8

Figure 17. Graph Window of VisualAnalog, NSR Enabled,

7.

The amplitude shows approximately 0.6 dB lower than

when the NSR is disabled. The NSR circuitry introduces

this loss. An amplitude of −1.6 dBFS with NSR enabled

is analogous to an amplitude of −1.0 dBFS with NSR

disabled.

8.

Repeat Step 3 to save the graph in a .csv file format.

Troubleshooting Tips

If the FFT plot appears abnormal, do the following:

If you see a normal noise floor when you disconnect the

signal generator from the analog input, be sure that you

are not overdriving the ADC. Reduce the input level if

necessary.

In VisualAnalog, click the

Settings

button in the

Input

Formatter

block (see Figure 7). Check that

Number

Format

in the settings of the

Input Formatter

block is set

to the correct encoding (offset binary by default). Repeat

for the other channel.

If the FFT appears normal but the performance is poor, check

the following:

Make sure that an appropriate filter is used on the

analog input.

Make sure that the signal generators for the clock and the

analog input are clean (low phase noise).

Change the analog input frequency slightly if noncoherent

sampling is being used.

Make sure that the SPI configuration file matches the

product being evaluated.

If the FFT window remains blank after

Run

(see Figure 12) is

clicked, do the following:

Make sure that the evaluation board is securely connected

to the

board.

Make sure that the FPGA has been programmed by

verifying that the

DONE

LED is illuminated on the

board. If this LED is not illuminated, make

sure that the U4 switch on the board is in the correct

position for USB CONFIG.

Make sure that the correct FPGA program was installed by

clicking the

Settings

button in the

ADC Data Capture

block in

VisualAnalog

. Then select the

FPGA

tab and

verify that the proper FPGA bin file is selected for the part.

If VisualAnalog indicates that the data capture timed out, do the

following:

Make sure that all power and USB connections are secure.

Probe the DCO signal at the ADC on the evaluation board

and confirm that a clock signal is present at the ADC

sampling rate.