PCI Bus Host Bridge

9-16

Élan™SC520 Microcontroller User’s Manual

■

Clock #6: The PCI host bridge master controller has synchronized the Am5

x

86 CPU

bus request and asserts req to gain access to the PCI bus.

■

Clock #7: The PCI host bridge gnt signal is sampled asserted, and the PCI bus is idle,

so FRAME is asserted to begin the PCI transaction. In this example, there is no arbitration

delay (the arbiter is parked on the host bridge). If another external PCI master was

granted the bus or the bus was not idle, FRAME assertion would be delayed until the

host bridge’s gnt was asserted and the bus was idle. Because the Am5

x

86 CPU is the

initiator of the cycle, the bus request signal is not seen externally.

■

Clock #9: The external PCI target asserts TRDY indicating it can accept the write data.

In this example, the PCI target did not add any wait states to the transaction. A PCI bus

Revision 2.2 compliant target can add up to 16 wait states that would delay the

transaction completion. A PCI bus target can also retry the PCI transaction. In this case,

the host bridge continues to generate the same transaction until the target returns TRDY

to complete the transaction. See Section 9.5.3.4.2 for information on retried

transactions.

■

Clock #10: The PCI host bridge samples TRDY asserted, which ends the PCI bus

transaction.

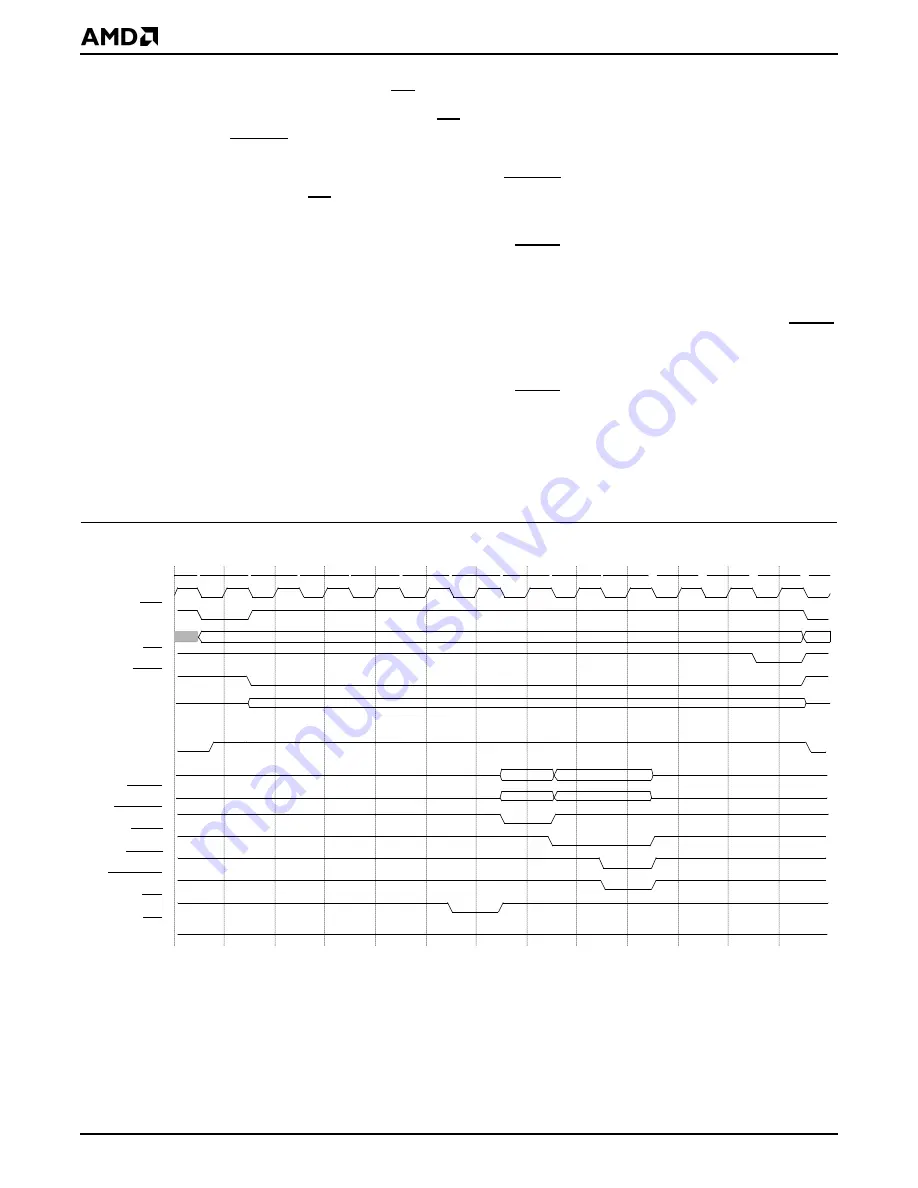

9.5.3.4.4

CPU Non-Posted Write Cycle to the PCI Bus

Figure 9-11 shows an Am5

x

86 CPU memory write cycle to the PCI bus with write posting

disabled. Figure 9-11 could represent any I/O or configuration write cycle.

Figure 9-11

Am5

x

86 CPU Non-Posted Write Cycle to the PCI Bus

Notes:

The clk signal denotes the 33-MHz clock source and represents both the CPU clock and the PCI clock. This diagram

does not represent the full synchronization of signals between these clock domains.

1

2

3

4

5

6

7

8

9

10

11

12

13

address

E\WHHQDEOHV

data out

GDWDRXW

ZULWHFPG

clk

ads

cycle_info

rdy

blast

CPU Data

pcihit

ADx

CBEx

FRAME

IRDY

TRDY

DEVSEL

req

gnt

Содержание Elan SC520

Страница 1: ...lan SC520 Microcontroller User s Manual Order 22004A...

Страница 4: ...iv lan SC520 Microcontroller User s Manual...

Страница 28: ...Introduction xxviii lan SC520 Microcontroller User s Manual...

Страница 42: ...Architectural Overview 1 14 lan SC520 Microcontroller User s Manual...

Страница 78: ...System Initialization 3 22 lan SC520 Microcontroller User s Manual...

Страница 108: ...Clock Generation and Control 5 10 lan SC520 Microcontroller User s Manual...

Страница 118: ...Reset Generation 6 10 lan SC520 Microcontroller User s Manual...

Страница 148: ...System Arbitration 8 24 lan SC520 Microcontroller User s Manual...

Страница 214: ...SDRAM Controller 10 36 lan SC520 Microcontroller User s Manual...

Страница 230: ...Write Buffer and Read Buffer 11 16 lan SC520 Microcontroller User s Manual...

Страница 288: ...GP Bus DMA Controller 14 22 lan SC520 Microcontroller User s Manual...

Страница 316: ...Programmable Interval Timer 16 8 lan SC520 Microcontroller User s Manual...

Страница 328: ...Software Timer 18 4 lan SC520 Microcontroller User s Manual...

Страница 346: ...Real Time Clock 20 12 lan SC520 Microcontroller User s Manual...

Страница 360: ...UART Serial Ports 21 14 lan SC520 Microcontroller User s Manual...

Страница 414: ...AMDebug Technology 26 8 lan SC520 Microcontroller User s Manual...