5–36

Chapter 5: Clock Networks and PLLs in Cyclone IV Devices

PLL Reconfiguration

October 2012

Altera Corporation

shows a functional simulation of the PLL reconfiguration feature.

1

When reconfiguring the counter clock frequency, the corresponding counter phase

shift settings cannot be reconfigured using the same interface. You can reconfigure

phase shifts in real time using the dynamic phase shift reconfiguration interface. If

you reconfigure the counter frequency, but wish to keep the same non-zero phase shift

setting (for example, 90°) on the clock output, you must reconfigure the phase shift

after reconfiguring the counter clock frequency.

Post-Scale Counters (C0 to C4)

You can configure multiply or divide values and duty cycle of post-scale counters in

real time. Each counter has an 8-bit high time setting and an 8-bit low time setting.

The duty cycle is the ratio of output high or low time to the total cycle time, that is the

sum of the two. Additionally, these counters have two control bits,

rbypass

, for

bypassing the counter, and

rselodd

, to select the output clock duty cycle.

When the

rbypass

bit is set to 1, it bypasses the counter, resulting in a divide by one.

When this bit is set to 0, the PLL computes the effective division of the VCO output

frequency based on the high and low time counters. For example, if the post-scale

divide factor is 10, the high and low count values are set to 5 and 5, to achieve a

50–50% duty cycle. The PLL implements this duty cycle by transitioning the output

clock from high-to-low on the rising edge of the VCO output clock. However, a 4 and

6 setting for the high and low count values, respectively, would produce an output

clock with a 40–60% duty cycle.

The

rselodd

bit indicates an odd divide factor for the VCO output frequency with a

50% duty cycle. For example, if the post-scale divide factor is three, the high and low

time count values are 2 and 1, respectively, to achieve this division. This implies a

67%–33% duty cycle. If you need a 50%–50% duty cycle, you must set the

rselodd

control bit to 1 to achieve this duty cycle despite an odd division factor. The PLL

implements this duty cycle by transitioning the output clock from high-to-low on a

falling edge of the VCO output clock. When you set

rselodd

= 1, subtract 0.5 cycles

from the high time and add 0.5 cycles to the low time.

For example:

■

High time count = 2 cycles

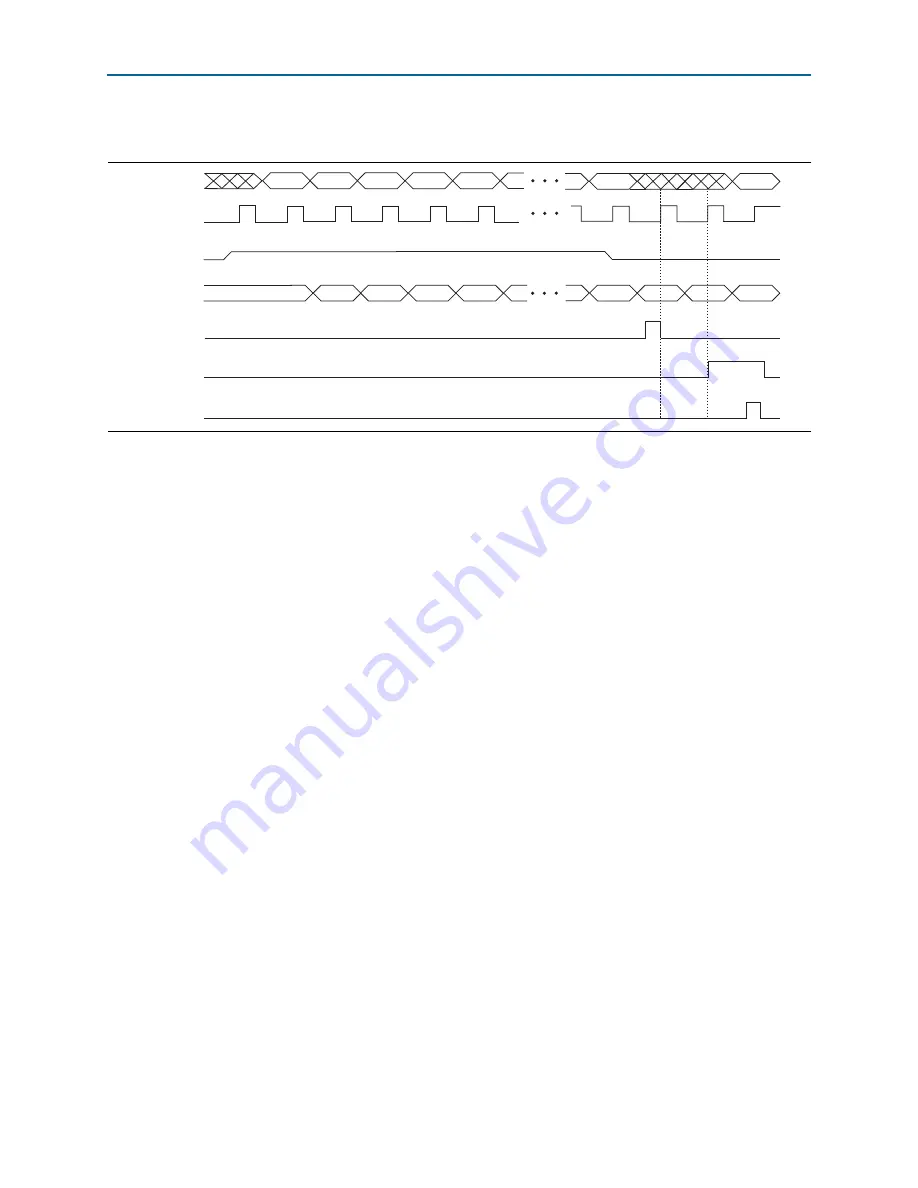

Figure 5–23. PLL Reconfiguration Scan Chain

scandata

scanclk

scanclkena

scandataout

configupdate

scandone

areset

D0_old

Dn_old

Dn

Dn (MSB)

D0 (LSB)

Содержание Cyclone IV

Страница 10: ...x Chapter Revision Dates Cyclone IV Device Handbook March 2016 Altera Corporation Volume 1...

Страница 14: ...I 2 Section I Device Core Cyclone IV Device Handbook March 2016 Altera Corporation Volume 1...

Страница 106: ...II 2 Section II I O Interfaces Cyclone IV Device Handbook March 2016 Altera Corporation Volume 1...

Страница 164: ...III 2 Section III System Integration Cyclone IV Device Handbook March 2016 Altera Corporation Volume 1...

Страница 274: ...vi Contents Cyclone IV Device Handbook February 2015 Altera Corporation Volume 2...

Страница 276: ...viii Chapter Revision Dates Cyclone IV Device Handbook February 2015 Altera Corporation Volume 2...

Страница 280: ...I 2 Section I Transceivers Cyclone IV Device Handbook February 2015 Altera Corporation Volume 2...

Страница 440: ...iv Contents Cyclone IV Device Handbook December 2016 Altera Corporation Volume 3...

Страница 442: ...vi Chapter Revision Dates Cyclone IV Device Handbook December 2016 Altera Corporation Volume 3...

Страница 446: ......