ADM-PA101 User Manual

north edge of the card.

Figure 11 : uSD Location

The ADM-PA101 is shipped with a simple PCIe endpoint bitstream which should be visible to the operating

system (using Windows Device Manager or “lspci” in Linux) in order to provide confidence that the card is

working correctly when installed in a system. On request, Alpha Data can pre-load custom bitstreams during

production test. Please contact [email protected] in order to discuss this possibility.

At power-on, the ACAP attempts to configure itself automatically according to the mode pins as described in

. Alpha Data ships these cards set to the uSD boot mode by default.

3.9.2.1 Building and Programming uSD Configuration Images

Find below the steps to get a bootable image file(BOOT.BIN) from your implemented example design,

•

Take the generated PDI file of your design(implementation folder of the project).

•

Create a text file of name '<my_design_name>.bif' with the following in it,

all: { image { { type=bootimage, file=<my_design>.pdi } } }

•

Now, run the following in the command line,

bootgen -arch versal -image <my_design_name>.bif -w -o BOOT.BIN

Note: You may first need to run settings32.bat/settings64.bat in your current Vivado installation path

(depending if yours is a 32 or 64 bits OS)

•

Prepare the uSD card by formatting it as a whole FAT partition.

•

Copy the obtained BOOT.BIN file into the uSD card.

The uSD card is now ready to be booted from, so you can insert it in the PA101 with the right boot mode in the

switches and turn it on. Your example design will be programmed in the FPGA automatically at boot.

3.9.3 Configuration via JTAG

A micro-USB AB Cable may be attached to the front panel or rear edge USB port. This permits the ACAP to be

reconfigured using the Xilinx Vivado Hardware Manager and Vitis via the integrated Digilent JTAG converter box.

The device will be automatically recognized in Vivado Hardware Manager and Vitis.

For more detailed instructions, please see “Using a Vivado Hardware Manager to Program an FPGA Device”

section of

Also, if you went through the section

Building and Programming QSPI Configuration Images

, you can program

the FPGA(xcvc1902 part) instead of the Flash attached to it. The HW setup is the same. You simply don't need to

turn OFF and ON the Host PC after programming the FPGA.

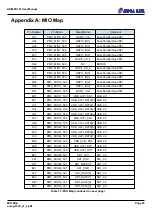

3.9.4 Boot Modes

Page 20

Functional Description

ad-ug-1430_v1_2.pdf