ASAHI KASEI

[AK4537]

MS0202-E-04

2005/04

-

63

-

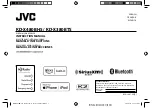

2. When X'tal is used in PLL mode. (Master mode)

MCKPD bit

(Addr:01H, D7)

BICK, LRCK

(Master Mode)

PS1-0 bits

(Addr:04H, D5-4)

PMXTL bit

(Addr:01H, D6)

PMPLL bit

(Addr:01H, D5)

MCKO bit

(Addr:04H, D3)

MCKO pin

XX

00

40msec(max)

Output

Output

(1)

20ms(typ) (2)

(3)

(4)

E x a m p le :

A u d io I/F F o r m a t : I

2

S

B IC K f re q u e nc y a t M a s te r M o d e : 6 4 f s

I np u t M a s t e r C lo c k S e le c t a t P L L M o d e : 1 1 .2 8 9 6 M H z

O utp u t M a s te r C lo c k F re q ue n c y : 6 4 f s

(1 ) A d d r:0 1 H , D a ta : 4 0 H

(2 ) A d d r:0 1 H , D a ta : 6 0 H

(3 ) A d d r:0 4 H , D a ta 6 A H

(4 ) M C K O , B I C K a n d L R C K o u t p u t s ta rts

Figure 50. Clock Set Up Sequence(2)

<Example>

(1) Release the pull-down of the XTI pin : MCKPD bit = “1”

o

“0” and and power-up the X’tal oscillator: PMXTL

bit = “0”

o

“1”

(2) Power-up PLL : PMPLL bit = “0”

o

“1”

The PLL should be powered-up after the X’tal oscillator becomes stable. It takes X’tal oscillator 20ms(typ) to

be stable after PMXTL bit=“1”. This time depends on X’tal. PLL needs 40ms lock time the PMPLL bit = “0”

o

“1”.

(3) Enable MCKO output : MCKO bit = “0”

o

“1” and set up MCKO output frequency (PS1-0 bits)

(4) MCKO, BICK and LRCK are output after PLL lock time.

electronic components distributor