Document number

205065

Version

Rev. N

Issue date

2019-02-04

Sirius OBC and TCM User Manual

Page

30

of

174

Return value

Description

0

Device closed successfully

5.3.2.3.

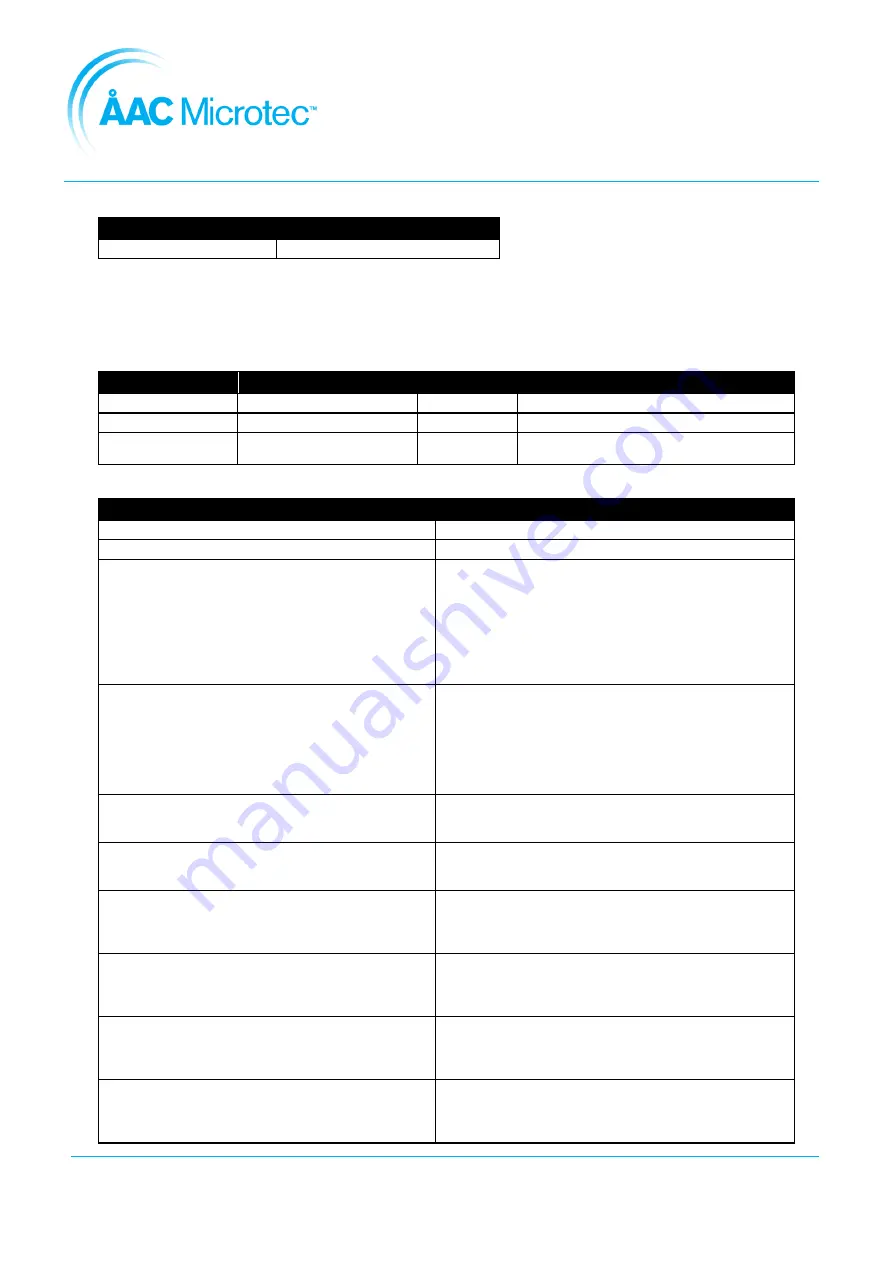

int ioctl(…)

Ioctl allows for disabling/enabling functionality of the error manager, setting of the timeout

and reading out counter values.

Argument name

Type

Direction

Description

fd

int

in

File descriptor received at

open

cmd

uint32_t

in

Command to send

val

uint32_t / uint32_t *

in / out

Value to write or a pointer to a buffer where

data will be written

Command table

Description

ERRMAN_GET_SR_IOCTL

Get the status register, see 5.3.2.3.1

ERRMAN_GET_CF_IOCTL

Gets the carry flag register, see 5.3.2.3.2

ERRMAN_GET_SELFW_IOCTL

Points to which boot firmware that will be loaded and

executed upon system reboot.

0x0: Programmable FW from Power on

0x1: Programmable FW, Backup copy

0x2: Programmable FW, Backup copy

0x3: Safe FW

0x4: Safe FW, Backup copy

0x5: Safe FW, Backup copy

ERRMAN_GET_RUNFW_IOCTL

Gets the currently running firmware

0x0: Programmable FW from Power on

0x1: Programmable FW, Backup copy

0x2: Programmable FW, Backup copy

0x3: Safe FW

0x4: Safe FW, Backup copy

0x5: Safe FW, Backup copy

ERRMAN_GET_SCRUBBER_IOCTL

Gets the state of the memory scrubber.

0 = Scrubber is disabled

1 = Scrubber is enabled.

ERRMAN_GET_RESET_ENABLE_IOCTL

Gets the reset enable state.

0 = Soft reset is disabled.

1 = Soft reset is enabled

ERRMAN_GET_WDT_ERRCNT_IOCTL

Gets the watchdog error count register.

This register can store a value up to 15 and then wraps.

After a wrap the WDT carry flag bit is set in the carry flag

register. see 5.3.2.3.2

ERRMAN_GET_EDAC_SINGLE_ERRCNT_IOCTL

Gets the EDAC single error count.

See 5.3.2.3.3 for interpretation of the register.

After a wrap the EDAC single error count carry flag bit is

set in the carry flag register. See 5.3.2.3.2

ERRMAN_GET_EDAC_MULTI_ERRCNT_IOCTL

Gets the EDAC multiple error count.

See 5.3.2.3.4 for interpretation of the register.

After a wrap the EDAC multiple error count carry flag bit

is set in the carry flag register. See 5.3.2.3.2

ERRMAN_GET_CPU_PARITY_ERRCNT_IOCTL

Gets the CPU Parity error count register.

This register can store a value up to 15 and then wraps.

After a wrap the CPU parity error count carry flag bit is

set in the carry flag register. See 5.3.2.3.2