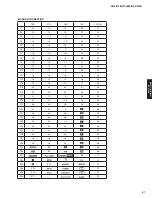

NAND-Flash Interface

Ethernet MAC-Phy Interface (MII)

Pin No.

Function Name

I/O

MII

RMII

SMII

U14

MIIDIO

I/O

Management data

Management data

V14

MIIMDC

O

Management clock

Management clock

V13

MIIRXD[3]

I

RxD 3

RxD 1

U13

MIIRXD[2]

I

RxD 2

RxD 0

V12

MIIRXD[1]

I

RxD 1

Rx-Sync

U12

MIIRXD[0]

I

RxD 0

RxD

T12

MIIRXCLK

I

Receive clock

Receive clock

R13

MIIRXER

I

Receive error

Receive error

T14

MIIRXDV

I

Receive data valid

Carrier sense/data valid

V11

MIITXD[3]

O

TxD 3

TxD 1

U11

MIITXD[2]

O

TxD 2

TxD 0

V10

MIITXD[1]

O

TxD 1

Tx-Sync

U10

MIITXD[0]

O

TxD 0

TxD

R12

MIITXCLK

I

Transmit clock

Transmit clock

T11

MIITXER

O

Transmit error

R11

MIITXEN

O

Transmit data enable

Transmit data enable

T13

MIICOL

I

MII ethernet collision

R14

MIICRS

I

MII carrier sense

V15

MIIPHYCLK

O

25.000 MHz clock

50.000 MHz clock

125.000 MHz clock

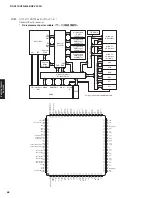

Pin No.

Function Name

I/O

Detail of Function

T17

T16

T15

R17

FD[7:0]

I/O

Bi-directional data bus.

R16

R15

P16

P15

V18

FALE

O

Address latch enable; pull-up/down defines boot mode.

U16

FCLE

O

Command latch enable; pull-up/down defines boot mode.

U15

NFCE0

O

Chip-enable, low-active.

U18

NFRB

I

Ready/busy. NAND flash is busy when NFRB is low.

V17

NFRE

O

Read enable, low-active.

U17

NFWE

O

Write enable, low-active.

V16

NFWP

O

Write protect, low-active.

Pin No.

Function Name

I/O

Detail of Function

H18

Chip select signals. The active memory range for NCS[n] (active low) can be configured.

J17

• NCS[0] supports SRAM, can be used for booting.

J16

NCS[3:0]

O

• NCS[1] supports SDRAM or SRAM.

J15

• NCS[2] supports SRAM.

• NCS[3] supports SRAM.

K17

NOE

O

Output enable, asserted (low) for read operations.

K16

NWE

O

Write enable, asserted (low) for write operations.

K18

NWAIT

I

External wait line. If NWAIT is asserted, memory access will be stalled. Can be configured as either low-

active (default) or high-active.

K15

MEMCLK

O

SDRAM system clock.

J18

MEMCKE

O

SDRAM clock enable.

75

RX-V475/HTR-4066/RX-V500D

RX-V475/HTR-4066/

RX-V50

0D

Summary of Contents for RX-V500D

Page 9: ...RX V500D A model RX V500D B G models 9 RX V475 HTR 4066 RX V500D RX V475 HTR 4066 RX V500D ...

Page 132: ... CONFIGURING THE SYSTEM SETTINGS RX V475 HTR 4066 RX V500D 133 ...

Page 133: ... システム設定を変更する RX V475 HTR 4066 RX V500D 134 ...

Page 146: ...147 RX V475 HTR 4066 RX V500D RX V475 HTR 4066 RX V500D MEMO ...

Page 147: ...RX V475 HTR 4066 RX V500D ...