FPGA Design Demonstration Board

Hardware User Guide

3-13

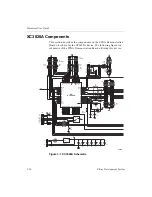

Figure 3-6 XC4003E Schematic

XC4003E FPGA and Socket (U5)

The XC4003E FPGA occupies socket U5 on the demonstration board.

6

1

1

1

2

4.7K

4

1

3

+5

1

2

1

2

1K

2

4

6

10

12

14

16

18

J2B

1

2

3

J10

3

4

5

6

1

9

1

7

2

1

2

1

2

1

2

1

2

1

2

1

LD101VR

2

1

2

1

5

6

7

8

INP3

1

1

6

INP

R4

1K

R5

1K

3

4

560

1

2

5

6

7

8

3

4

1

2

560

PGCK1

13

I/O

14

TDI-I/O

15

TCK-I/O

16

TMS-I/O

17

I/O

18

I/O

19

I/O

20

I/O

23

I/O

24

I/O

25

I/O

26

I/O

27

I/O

28

SGCK2

29

M1

30

M0

32

PROG

55

I/O

56

PGCK3

57

I/O

58

I/O

59

I/O

60

I/O

61

I/O

62

I/O

65

I/O

66

I/O

67

I/O

68

I/O

69

I/O

70

DIN

71

DOUT

72

CLK

73

U5

XC4003E

O

U

T

8

N

C

1

Y1

1

2

1K

3

4

5

6

7

8

1

2

1K

3

4

5

6

7

8

1

8

4.7K

DATA

1

CEO

6

CE

4

CLK

2

OE/R

3

U2

1765

7

1

0

RST

1

6

1

+5

5

27K

1

2

1

7

1

8

1

4

1

9

1

3

9

11

13

15

17

7

J2A

1

2

J7

CUT

OPTION

1

2

560

3

4

7

8

5

6

3

4

5

6

7

8

1

2

560

1

2

560

3

4

7

8

1

2

560

3

4

5

6

5

6

7

8

2

15

MPE

3

14

SPE

R3

100K

8

9

INIT

D17

MBR030

8

7

3

6 4 2

1 9

1

0 5

+5

U7

HPSP5551

SW4

RESET

SW6

PROG

SW5

SPARE

8

7

3

6 4 2

1 9

1

0 5

U8

U1, U2

U3

U4

U5

7, 8

+5

GND

3

18, 52

2, 11, 33, 42, 54,

63, 74

5

2

1, 35

1, 12, 21, 31, 43, 52,

43, 52, 64, 76

HPSP5551

TDI

TCK

TMS

CLKI

TRIG

RD

RT

CLKO

VCC

GND

CCLK

DONE

PROG

INIT

RST

DIN

SW2

RN2

RN4

RN8

RN19

RN18

SW1

RN4

D9

D16

SW2

SW2

SW2

RN12

RN15

RN13

RN14

SW2

RN3

RN9

+5

TDO

I/O

PGCK4

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

SGCK1

M2

PGCK2

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

SGCK3

DONE

X4728

0I/O

1I/O

2I/O

3I/O

4I/O

5I/O

6I/O

7I/O

8I/O

9I/O

10I/O

11I/O

12I/O

13I/O

14I/O

15I/O

10

9

8

7

6

5

4

3

84

83

82

81

80

79

78

77

75

34

35

36

37

38

39

40

41

44

45

46

47

48

49

50

51

53