38

www.xilinx.com

1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Chapter 4:

Designing with the Core

R

-- DISCONTINUED PRODUCT --

See also

Appendix C, “Calculating DCM Phase-Shifting”

to meet Spartan-3, Spartan-3E

and Spartan-3A device setup and hold requirements for external GMII.

Keep it Registered

To simplify timing and increase system performance in an FPGA design, keep all inputs

and outputs registered between the user application and the core. This means that all

inputs and outputs from the user application should come from, or connect to, a flip-flop.

While registering signals may not be possible for all paths, it simplifies timing analysis and

makes it easier for the Xilinx tools to place-and-route the design.

Recognize Timing Critical Signals

The UCF provided with the example design identifies the critical signals and timing

constraints that should be applied. See

Chapter 9, “Constraining the Core”

Use Supported Design Flows

The core is pre-synthesized and delivered as an NGC netlist. The example implementation

scripts provided use XST 11.1 as the synthesis tool for the HDL example design. Other

synthesis tools may be used for the user application logic. The core is always unknown to

the synthesis tool and should appear as a black box. For post synthesis, only ISE® 11.1 tools

are supported.

Make Only Allowed Modifications

The GEMAC core should not be modified by you. Any modifications may have adverse

effects on system timing and protocol compliance. Supported user configurations of the

GEMAC core can only be made by selecting the options in the CORE Generator when the

core is generated. See

Chapter 3, “Generating the Core.”

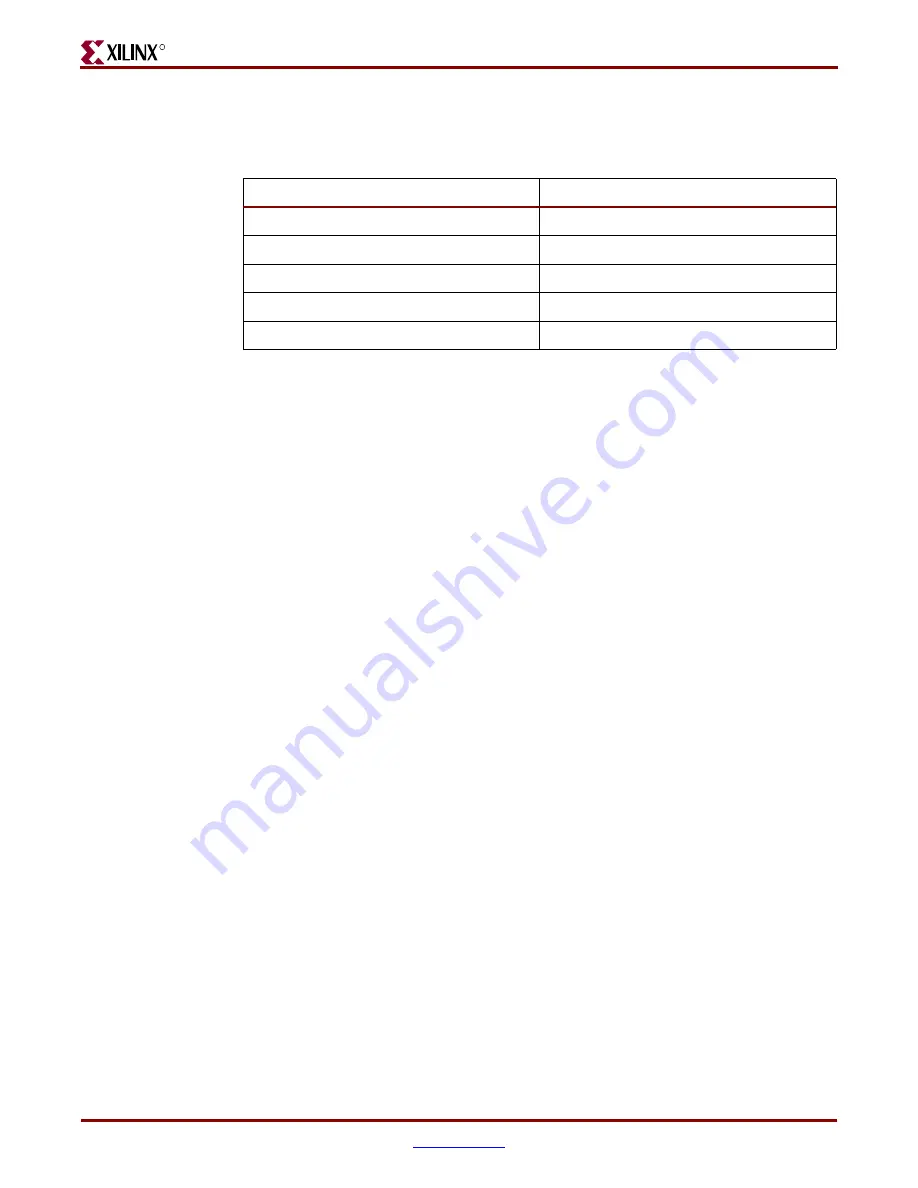

Table 4-1:

Degree of Difficulty for Various Implementations

Device Family

Difficulty

Spartan-3A/3AN/3A DSP platforms

Difficult

Spartan-3E platform

Difficult

Spartan-3 device

Difficult

Virtex-4 device

Easy

Virtex-5 device

Easy