NINA-W1 series - System integration manual

UBX-17005730 - R15

System description

Page 6 of 54

C1 - Public

1.2

Architecture

1.2.1

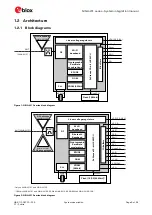

Block diagrams

Figure 1: NINA-W13 series block diagram

* Only on NINA-W101 and NINA-W102.

** 16 Mbit

NINA-W101 and NINA-W102; 32 Mbit NINA-W106-00B; 64Mbit NINA-W106-10B

Figure 2: NINA-W10 series block diagram

(NINA-W131)

Flash (16 Mbit)

Linear voltage regulators

RF

ROM

Wi-Fi

baseband

IO

b

u

ff

ers

2

xX

ten

sa

3

2

-bi

t L

X

6

MC

U

SRAM (4Mbit)

Cryptographic

hardware

accelerations

PIFA antenna

(NINA-W132)

PLL

Quad SPI

VCC_IO

VCC (3.0-3.6 V)

40 MHz

Reset

UART

RMII

EFUSE

GPIO

BPF

ANT

SPI

Flash (16/32/64 Mbit)**

Linear voltage regulators

RF

ROM

Wi-Fi

baseband

Bluetooth

Baseband

IO

b

uffer

s

2

xX

ten

sa

3

2

-bi

t L

X

6

MC

U

SRAM

(4Mbit)

Cryptographic

hardware

accelerators

PIFA antenna

(NINA-W102)

PLL

Quad SPI

VCC_IO

VCC (3.0–3.6 V)

40 MHz

Reset

ANT (NINA-W101)

UART

RMII

I2C

SPI

SDIO

Quad SPI

JTAG

GPIO

ADC/DAC

EFUSE

CAN

BPF*

LPO

(NINA-W106)

PCB trace antenna