TE0600 TRM

Revision: V3.02

Copyright © 2017 Trenz Electronic GmbH

Page

of

10

33

http://www.trenz-electronic.de

Power Supervision

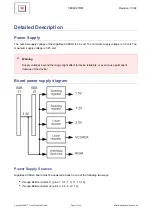

Power-on Reset

During power-on, the /RESET line is first asserted. Thereafter, the supply voltage supervisor monitors the

power supply rail 3.3V and keeps the /RESET line active (low) as long as the supply rail remains below the

threshold voltage (2.93 volt). An internal timer delays the return of the /RESET line to the inactive state

(high) to ensure proper system reset prior to a regular system start-up. The typical delay time td of 200 ms

starts after the supply rail has risen above the threshold voltage.

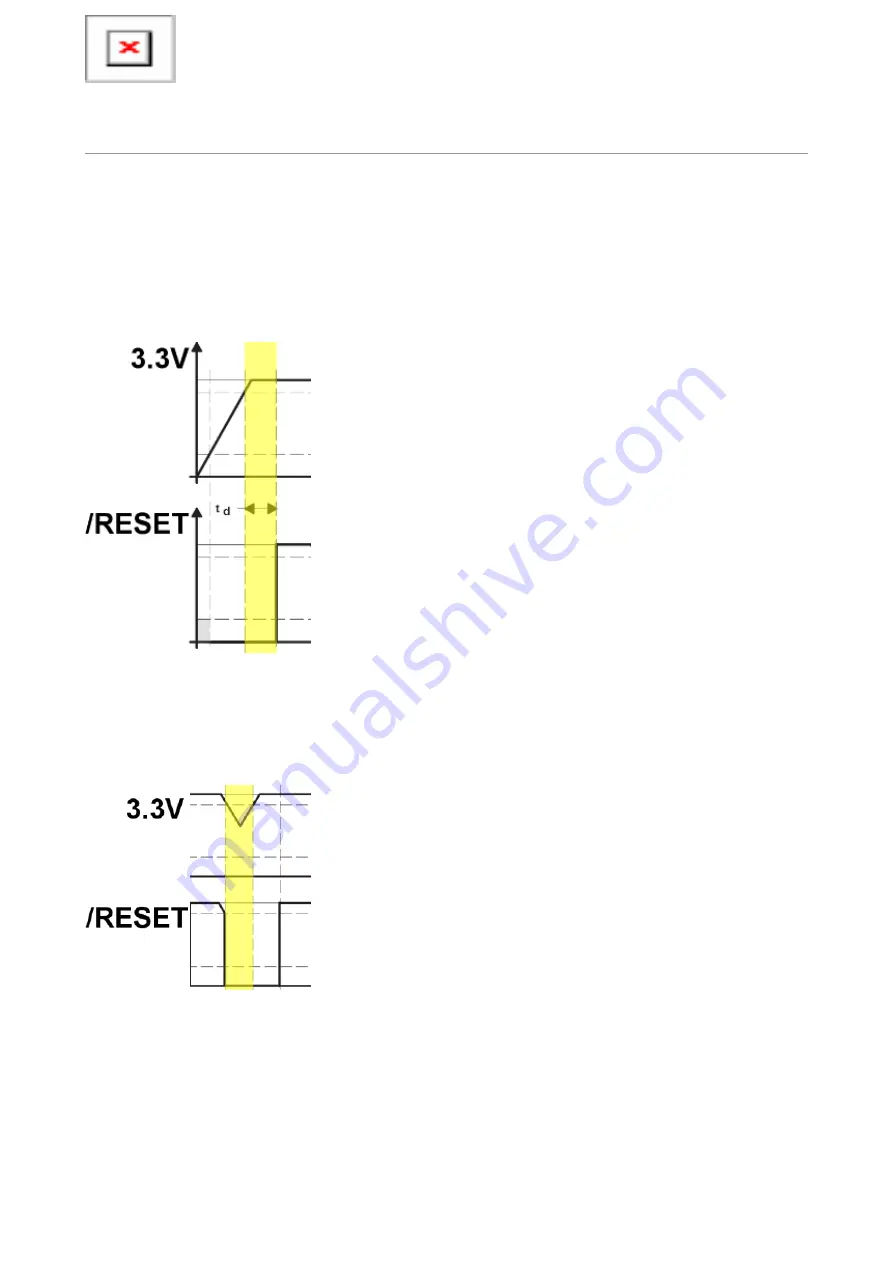

After this delay, the /RESET line is reset (high) and the FPGA configuration can start. When the supply rail

voltage drops below the threshold voltage, the /RESET line becomes active (low) again and stays active

(low) as long as the rail voltage remains below the threshold voltage (2.93 volt). Once the rail voltage raises

again and remains over the threshold voltage for more than the typical delay time td of 200 ms, the /RESET

line returns to the inactive state (high) to allow a new system start-up.