User's Manual l MBa8MPxL UM 0100 l © 2022, TQ-Systems GmbH

Page 20

Table 15:

Pinout LVDS control, X7

3.3.9

LVDS

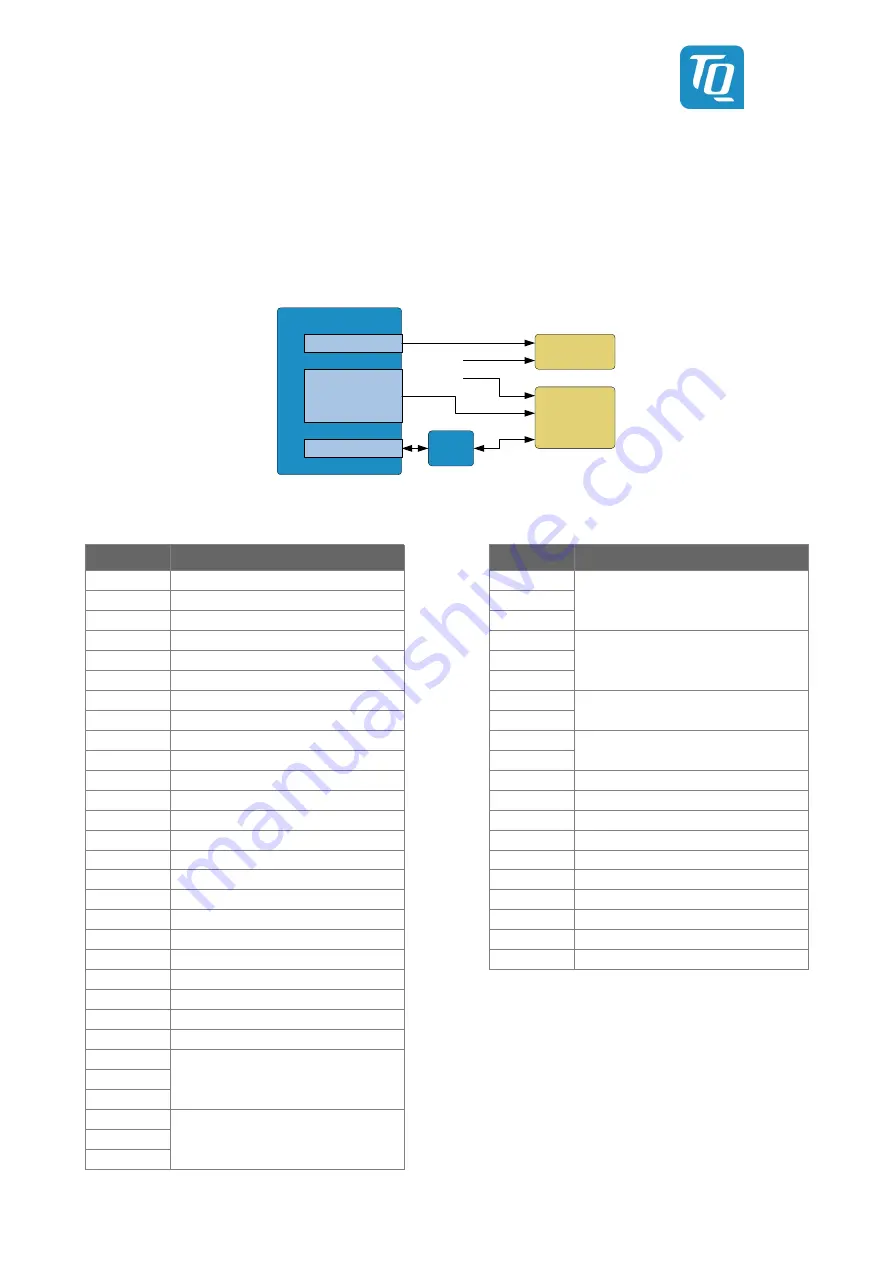

The i.MX 8M Plus offers an LVDS controller with a dual LVDS interface. Each of the interfaces uses four differential lanes.

On the MBa8MPxL there is one interface for connecting single or dual LVDS. In addition, two GPIO (BLT_EN, RESET#), a PWR_EN

and a PWM signal are provided. GPIO3_IO14, GPIO3_IO19, GPIO3_IO20 and GPIO3_IO21 are used for these four 1.8 V signals.

If required, the signal PWM2 can be multiplexed on the same CPU pin instead of GPIO3_IO21.

Both DF19 LVDS connectors - Data and CMD - are placed on the bottom side of the MBa8MPxL.

The USB signals of the CMD connector are connected to port 4 of the USB 3.0 hub.

RESET, BLT_EN,

PWR_EN,

CONTRAST/PWM

TQMa8MPxL

LVDS0 (CH0/CH1)

LVDS Data

USB

LVDS – Control

5 V / 3.3 V

GPIO3_IO14

GPIO3_IO[19:21]

5 V / 12 V

USB

3.0 Hub

Figure 17: Block diagram LVDS

Table 14:

Pinout LVDS data, X11

Pin

Signal

Pin

Signal

1

LVDS0_CH0_TX0_N

1

12 V

2

LVDS0_CH0_TX0_P

2

3

LVDS0_CH0_TX1_N

3

4

LVDS0_CH0_TX1_P

4

DGND

5

LVDS0_CH0_TX2_N

5

6

LVDS0_CH0_TX2_P

6

7

GND

7

5 V

8

LVDS0_CH0_CLOCK_N

8

9

LVDS0_CH0_CLOCK_P

9

DGND

10

LVDS0_CH0_TX3_N

10

11

LVDS0_CH0_TX3_P

11

V_VBUS30_H4

12

LVDS0_CH1_TX0_N

12

DGND

13

LVDS0_CH1_TX0_P

13

USB30_H4_DN

14

GND

14

USB30_H4_DP

15

LVDS0_CH1_TX1_N

15

DGND

16

LVDS0_CH1_TX1_P

16

LVDS0_RESET#, 10 kΩ PD

17

GND

17

LVDS0_BLT_EN, 10 kΩ PD

18

LVDS0_CH1_TX2_N

18

LVDS0_PWR_EN, 10 kΩ PD

19

LVDS0_CH1_TX2_P

19

LVDS0_PWM

20

LVDS0_CH1_CLOCK_N

20

DGND

21

LVDS0_CH1_CLOCK_P

22

LVDS0_CH1_TX3_N

23

LVDS0_CH1_TX3_P

24

GND

25

V_5V_LVDS0

26

27

28

V_3V3_LVDS0

29

30